- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

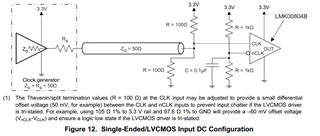

In TI's 4xAWR2243 cascaded imaging radar reference design TIDEP-01012 reference design | TI.com, the LMK00804B's nCLK input is DC-biased to 0.7V with resistor ladders as below:

the 40M_BUF_ IN_ PRIMAWRY clock is from AWR_1_OSC_CLKOUT, which is a gound to 1.4V swinging square wave.

And I was little confued about the input DC-bias, WHY the Non-inverting differential clock input is not DC biased to 0.7V? Isn't it supposed to both differential clock inputs are DC-biased?

Hi Andy,

Non-inverting input biased in the datasheet is done to reduce the input swing of 3.3 V to stay in the single ended swing requirements of the buffer. In this example we don't need that because swing is well below the datasheet requirements (based on VID specs). One other thing to notice is that they have a slight offset between inputs which keeps outputs low when there is no clock.

Best,

Asim