Other Parts Discussed in Thread: CLOCKPRO

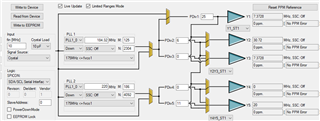

I am using your clock pro 1.2.1 software to generate three clock 20MHz, 7.3728Mhz and 30.72MHz from 10Mhz input clock, software selected CDCE925pwr chip and assigned these three signal to Y5, Y3, and Y1 with all 0 ppm error. Such as 7.3728MHz assigned to Y3 with "0 ppm" and "No PPM error" message, but if I set PDIV2 also 25, as same as PDIV3, Y2 is changed to 7.3728MHz, but message under it is "infinit ppm" and "0", does it mean Y2 also has 0 ppm error?

if I used software wizard to generate four clock 20MHz, 7.3728Mhz and 30.72MHz, 7.3728MHz, software generate 30.72Mhz and 7.3728 Mhz together from same source, not two 7.3728MHz together, any special reason for it? thanks.