Other Parts Discussed in Thread: ADC32RF45,

We are trying jesd interface between adc32rf45 and stratix 10 intel fpga, but we are not able to acheive link between adc and fpga.

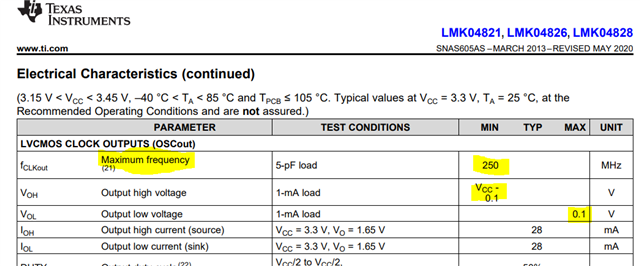

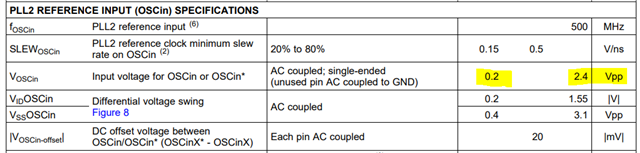

So, we tried jesd ip core with loopback condition, but we are not able to get the ATX PLL(ip core) lock output using the transciever clock(one of the output clock from lmk04828) as input reference clock.

As lock is not happening,we are not sure that transciever clock is stable.

So, we have done some tests to check the clock stablity.

Below we have attached our LMK configuration and test results for checking stability.

Can someone please tell us that what could be the issue for not locking.