Other Parts Discussed in Thread: CDCE913

【question】

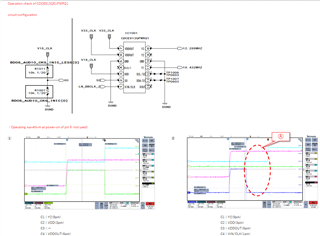

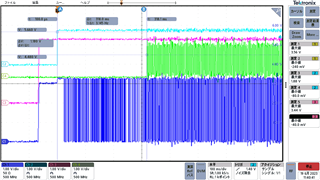

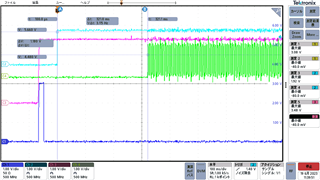

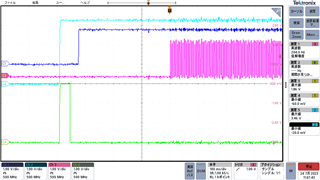

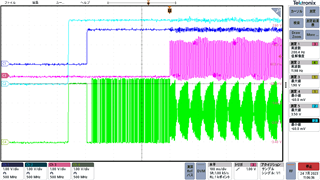

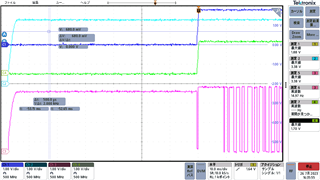

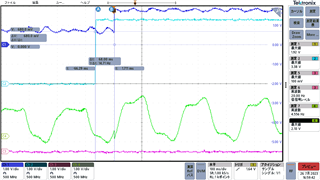

・Regarding part Ⓐ indicated by the dashed red circle, the waveform of board 1 in ① and the waveform of board 2 in ② have different timings when Y2 (9pin) falls from H to L. Why? mosquito?

・I can understand the movement of Y2 (9pin) from H to L in the waveform of board 1 in (1) (changes to L when VDD (3pin) turns ON), but in the waveform of board 2 in (2) It is unclear why the timing of Y2 (9pin) changing from H to L is this timing. Please tell me why this is the timing.