Other Parts Discussed in Thread: LMK04828, LMK04906

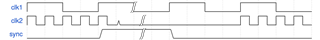

I have an application where I need to halt one of two clocks for a while (during a complex IO reset process) and then bring the clock back synchronously with the other clock (which must not be halted), maybe something like the figure below:

Is this possible?

As far as I can tell I can only stop selected clocks for any extended period of time using the SPI interface, which of course doesn't give me any control over the timing of the restarted clock.