Hello

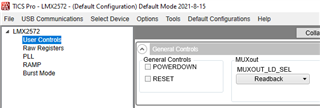

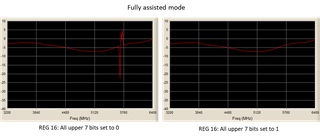

We have a design that uses the LMX2572 with full assistance. This works but not reliably. The problem appears to be the value read from register 112 (VCO DAC) during calibration. From the data sheet the upper 7 bits would be expected to be all 0s. However, most chips return all 1s. Some chips (that give us problems) return 0 for bit 11 others 0 for bit 15. If we use these values then we find the chip does not lock over some parts of the band. If we simply force all 7 bits to 1 then all appears OK. Generally we see the problem around 5.4 GHz.

We have not tested a large enough number of chips to give us confidence that our solution is reliable. Particularly as the solution is not in line with the data sheet.

So, my question is whether anyone else has come across this problem and if so, how it was solved.

Thank you.