Other Parts Discussed in Thread: LMX2492EVM

We are using the LMX2491 in combination with a 24GHz Radar Frontend what has a divide by 16 output for an FMCW radar. For this we need the ramp/chirp feature of the PLL chip itself. I've now optimized the loop filter for CW to get a tradeoff between phase noise and spur suppression but when I switch to a 30M ramp I can clearly see some discontinuties in the TX signal of the frontend.

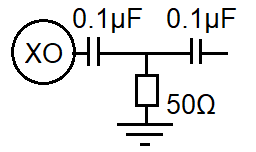

Here is the PLL simulation:

And here the settings what I use for the TICS:

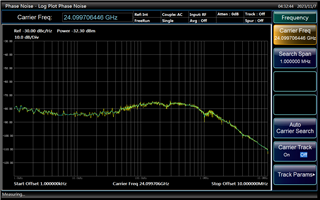

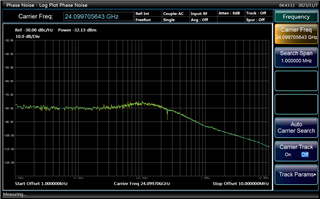

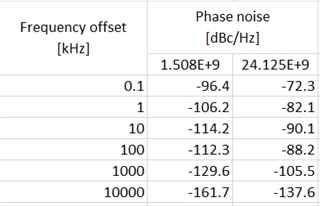

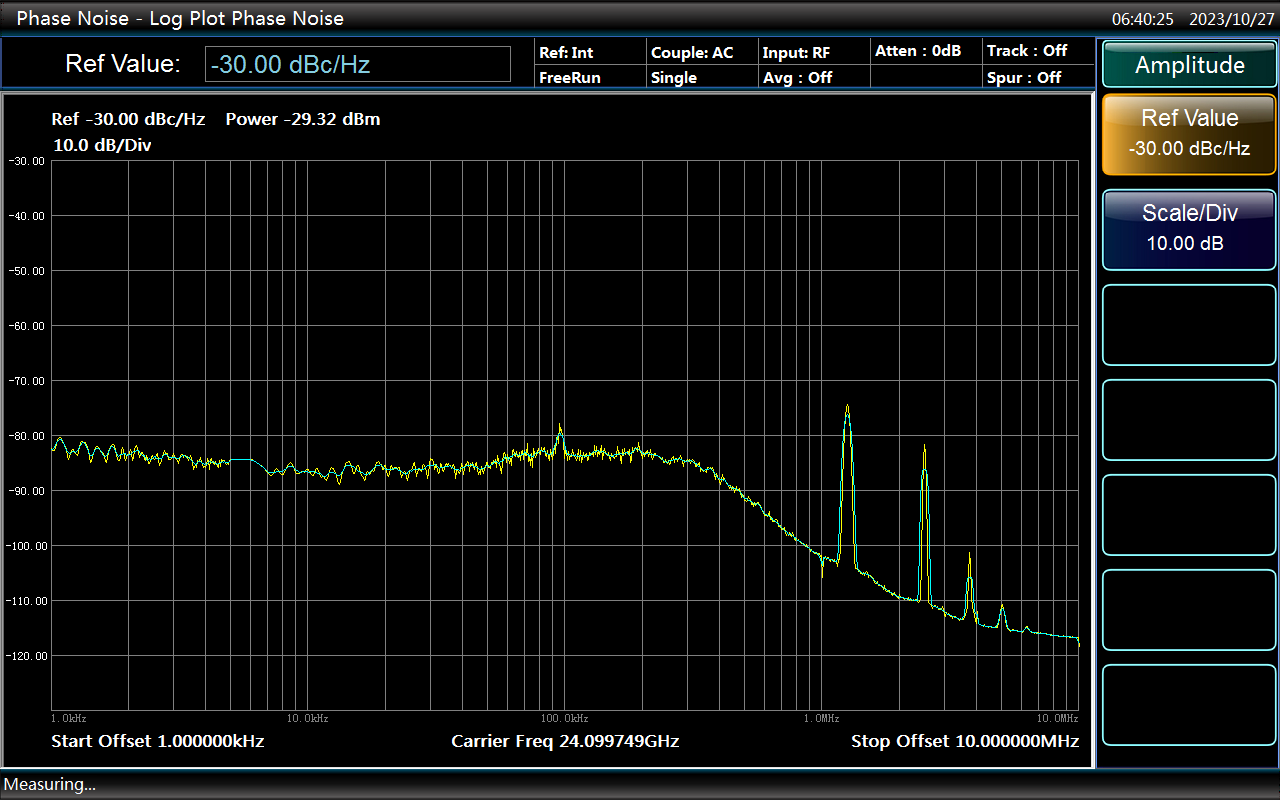

Here is the phase noise plot in CW mode for 24.1GHz TX:

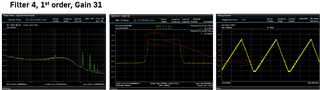

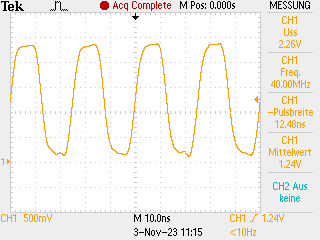

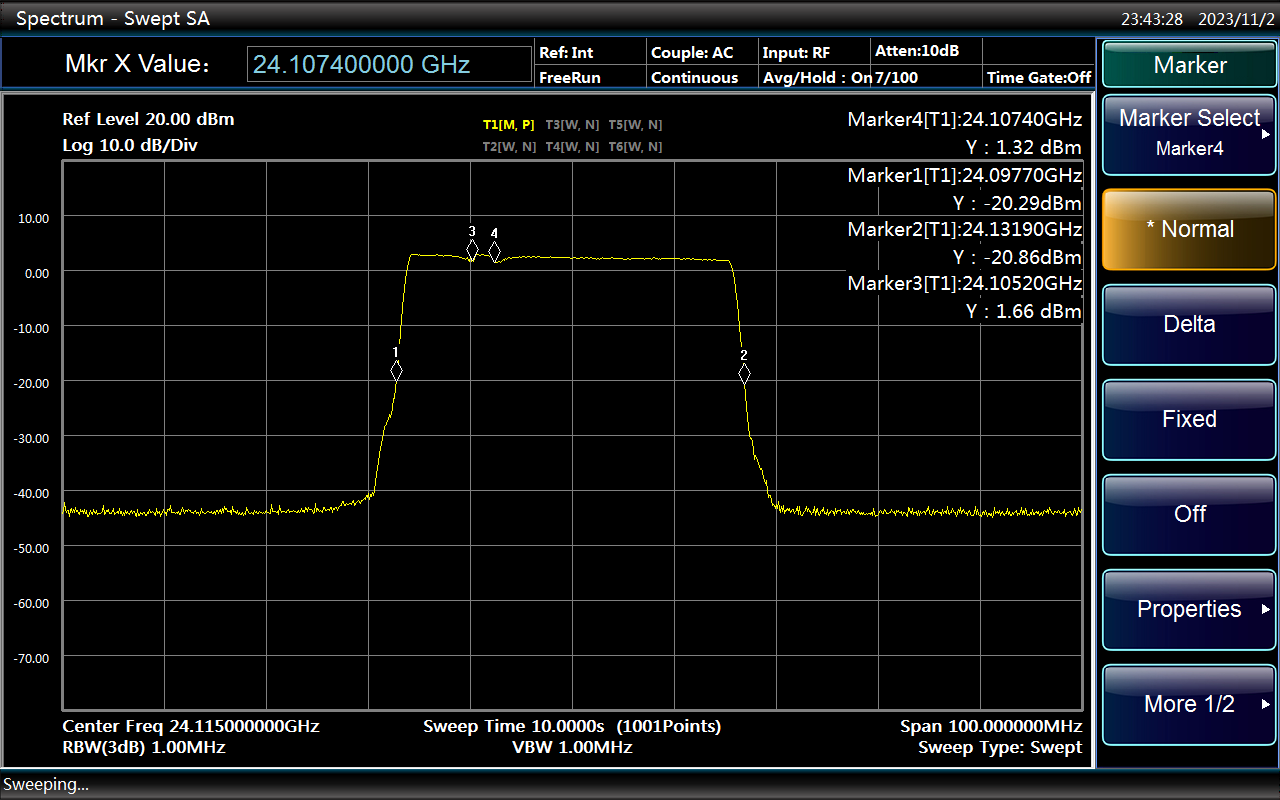

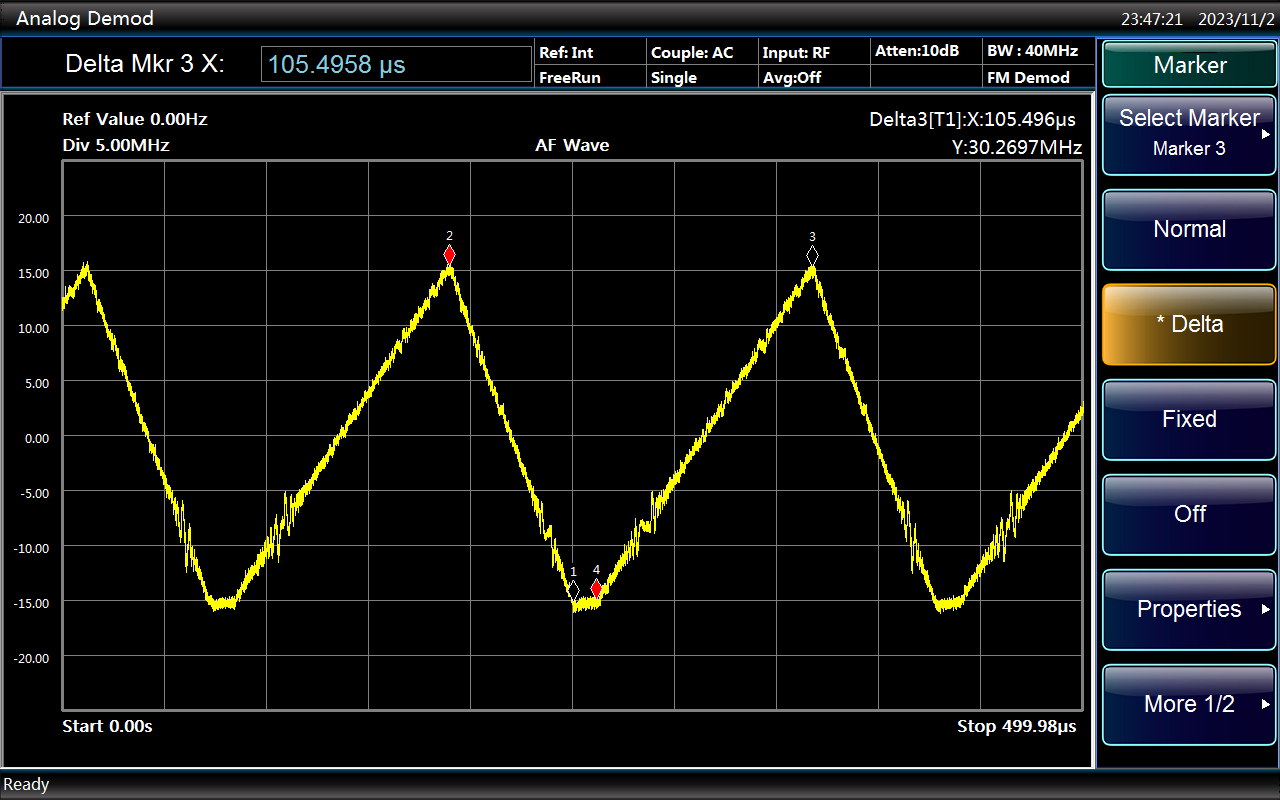

And here is the measured TX power over time and a demodulated measurement for the ramp:

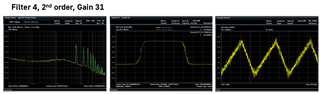

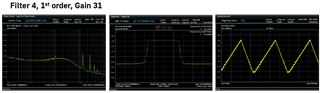

I've tried different settings and noticed that a lower charge pump gain will give me also less spurs and noise in the ramp itself. Further I tried to work with different FRAC_ORDERS but only order one is working in my setup. As soon as I use order 2 or 3 it looks like the loop filter gets unstable.

Does anyone have any idea what the reason could be for this behaviour?