Hello,

We like to use the PLL LMX2572. We use the LMX2572EVM and the our custom driver.

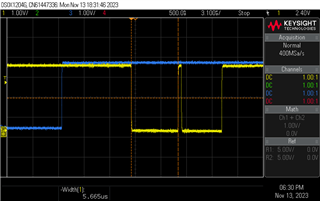

We observe a different behaviour of Muxout pin according to the LD_TYPE mode (R59). In mode 0 (VCO), we observe the expected behaviour. However, in mode 1 (VCO+VTUNE), we observe a questionnable behaviour of the MUXOUT pin.

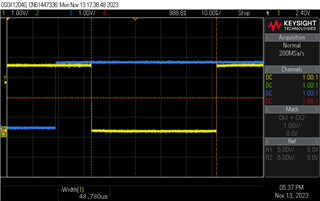

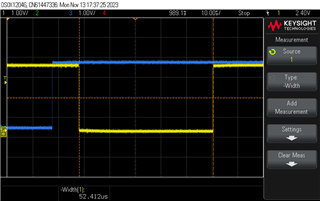

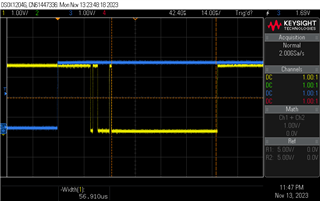

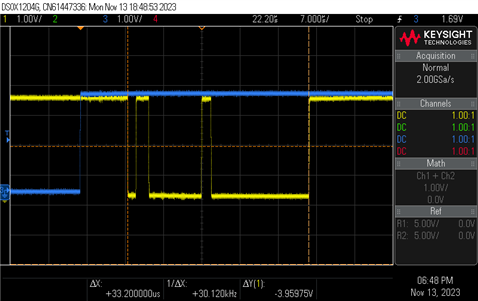

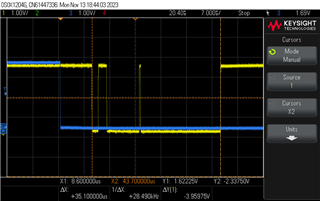

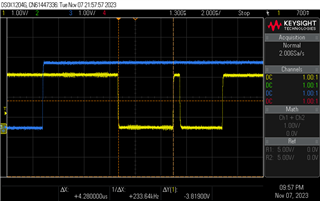

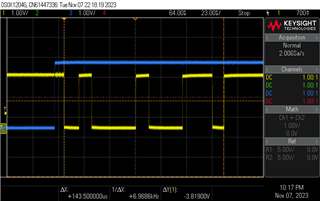

The MUXOUT pin is the yellow signal.

OSCIN = Fpd = 100MHz, RFOutA = 3.3GHz, Full assist mode, LD_TYPE = 1

OSCIN = Fpd = 10MHz, RFOutA = 3.3GHz, Full assist mode, LD_TYPE = 1

In mode Partial assist, we observe the same questionnable behaviour (only if LD_TYPE=1).

Is this behaviour normal ?

We have an additionnal question, in the LMX2572 datasheet, the R0 ADD_HOLD field use for block programming is not detailed in section 7.5.4 p 22, do we need set it for block programming ? It seems to work even if we keep it to 0.

Thanks in advance for your answers.

Best regards,

Malo