Other Parts Discussed in Thread: LMX2592,

Hello!

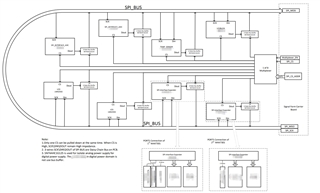

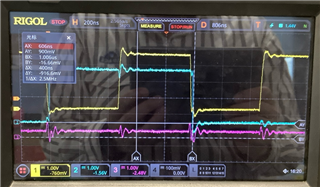

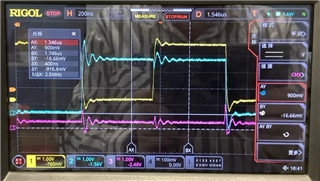

We use SPI bus to control and configure devices in system, all devices connect to SPI bus are daisy-chain topology. There are two LMX2592 chips ,one LMX2572LP chips and other 5 devices on the SPI bus. But after configuration, only the LMX2592 and LMX2572LP were not succssfully configured, the other 5-deviecs can be configured correctly. The read back data of LMX-devices on MUXOUT pin are all 0xFFFF. In this situation , configuration failtue is inevitable, the curve of SCK and MOSI likes this . I think the time sequence of SCK and MOSI is perfect , the voltage ringing on the rising & falling edges are in threshold of input.