hello. I'm Su-Yeong.

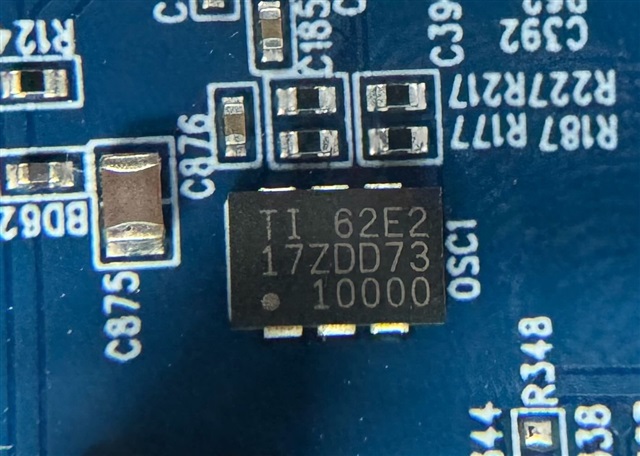

We are currently using 'LMK62E2-100M00SIAR', and our schematic is as shown below,

with NC and OE pins tied high at the same time as VDD.

My question is as follows

1. Does the NC pin have no circuit inside? If it is tied High like our schematic, does it affect the behavior?

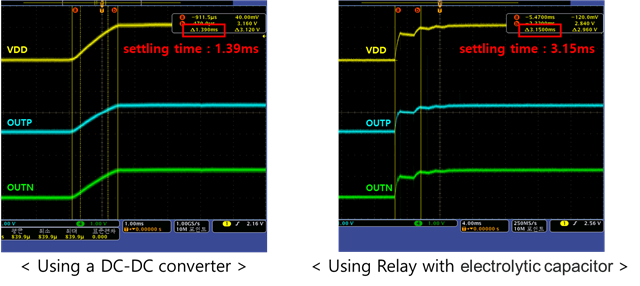

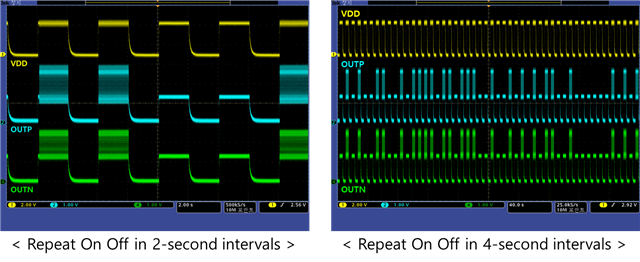

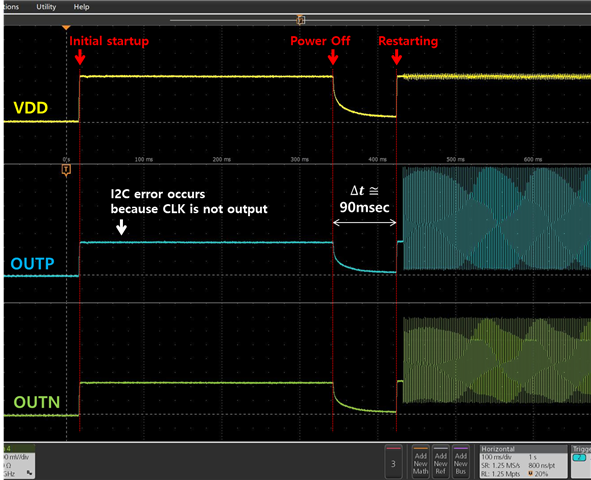

2. The OE pin is tied High at the same time when the power is turned on. Is there a power sequence that VDD and OE should follow?

Thanks.