Does the 1G output enable disable the output buffer to allow 2 different LMK1C1102 devices to drive the same signal - as in the pic below? Is it a Hi-Z output when disabled or driven low? I'm trying to select between 2 different clocks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Does the 1G output enable disable the output buffer to allow 2 different LMK1C1102 devices to drive the same signal - as in the pic below? Is it a Hi-Z output when disabled or driven low? I'm trying to select between 2 different clocks.

Don,

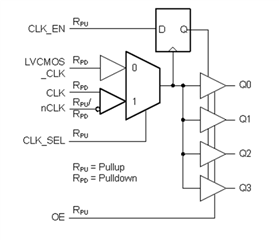

When the output is disabled the output will be driven low. This means that at the node where clock 1 and 2 meet, there could be a DC voltage coming out of the disabled output of up to 0.2 x VDD, which could cause problems on the LVCMOS receiver side of wherever your clock signal is going. A better option would be to use a buffer with an input multiplexer like the LMK00804B.

Regards,

Will