Other Parts Discussed in Thread: LMK04832

Hello,

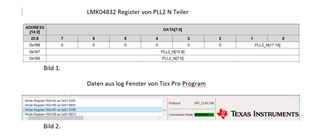

when we are using on of the newer TICSPRO versions (tested with 1.7.6.2, 1.7.7.1, 1.7.7.2 ) for loading a setup into our LMK04832 evauation board the PLL2 does not lock. We have to manually set the N-Divider value to a wrong value and set the correct afterwards to get the lock.

We have one PC with an old version 1.7.0. There the register writing takes much more time, but in the end when all registers a written the PLL2 locks correctly.