Other Parts Discussed in Thread: LMK6H

Hi Support

We would like to check if jitter specification of LMK62I0-100M could meet PCIe gen6 application. Please help to check.

Requirements :

1. package size: 5*3.2 mm

2. frequency : 100MHz

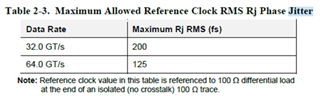

3. Jitter:

Please let me know if you need more specification.