Tool/software:

Dear team,

Attached Schematics of LMK clock for ADC IC. Please review and provide feedback for the same.

<attachment deleted>

Regards,

Kaushal

Kaushal,

You posted documents with confidentiality markers on them, so I deleted them from your post. In the future, please do not post documents with confidentiality markers on public forums

Edited: apologies, I got my symbols on poster names mixed up and thought this was coming from a TI internal source as opposed to an external source. Please disregard prior notice - it's your schematic, if you can post it here that's at your discretion.

That said, I have reviewed the schematic before deletion, and I see no issues.

Regards,

Derek Payne

Derek

Thankyou for schematics review of LMK04828 clock. We will continue with the current design and release

Regards,

Kaushal

Hi,

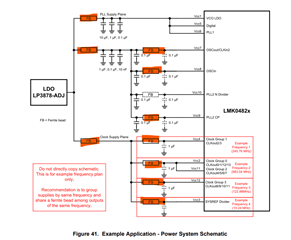

Also there are multiple ferrite recommended in datasheet for LMK power input as shown in picture below

Are these really required as we have not added in our circuit attached previously, which was said to have no issues. Can you please confirm the same?

Regards,

Kaushal

Strictly speaking, they are not required to get functional output clocks. They may be required to get high-performance, low-noise output clocks.

The LMK0482x has many internal LDOs to filter spurious influences in the <20MHz range, and on-chip bypass capacitance and bondwire inductance that forms low-pass filters cutting off spurious noise in the >200MHz range. Broadly speaking, these numbers can vary a bit, but the key takeaway is that there is an interval of about a decade from low 10s of MHz to low 100s of MHz where there are no mechanisms on-chip to filter out spurious influence.

In the end, the decision of how many ferrite beads to use comes down to your application's tolerance for spurious noise. If you need the best performance you can get, place the ferrites to isolate dissimilar 10-200MHz signals from each other. You can relax the ferrite requirements if your application is tolerant to spurs, or has lax jitter requirements (e.g. digital clocks that just need distinct monotonic signals). I generally advise people to at least place some footprints for ferrite beads, and if you don't need them you can put 0Ω resistors in instead - the overall cost difference is pretty negligible if it turns out you don't need these components, and is much cheaper than a re-spin of the PCB if it turns out you do need them.