Tool/software:

Hello,

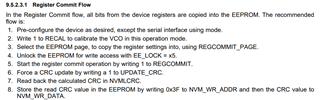

I am currently trying to load a configuration into the EEPROM of a CDCE6214Q1 with direct access flow.

When rebooting, the CDCE loads the configuration we want from its EEPROM (correct outputs/frenquencies) and the NVMLCRC updates but not the NVMSCRC, which stays at 0x0000.

I have looked at a similar thread: https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1282169/cdce6214-q1-cdce6214-q1

but the UPDATE_CRC R3[12] / power cycles don't change it, no matter how much times I do it.

I have this problem on 2 devices with different configurations.

Do you have any idea of what could be the reason here please?

Regards,

Alexandre