- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

PFA - for our PLL implementation. PLL output clock from channel A is 900MHz.

Crossover freq is 3600MHz.

In this case, can you please suggest how the discretes attached to CPOUT and VTUNE needs to be tuned?

Thanks

Hi Nandini,

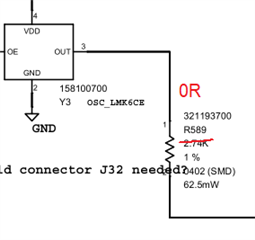

Since the supply to the LMK6C is 1.8V, its output should be 1.8V clock. R589 should be 0Ω.

Loop filter design depends on your application need, you can use PLL Sim (https://www.ti.com/tool/PLLATINUMSIM-SW) to design the filter.