Other Parts Discussed in Thread: LMK04832

Tool/software:

Hi team,

While we are going through our LMK04828 analog delay function, there is some confusing items, pls help to review and clarify the right understanding.

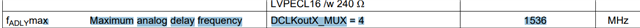

There is a max analog delay frequency spec to be 1536MHz:

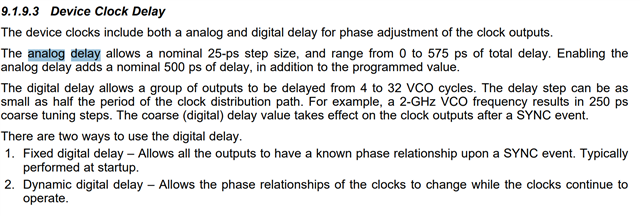

Besides, there is also another description in the detailed function introduction with the content: 25ps analog delay, and total 500ps analog delay range.

So how do we understand the two different description here?

For our application requirement, a 2.5GHz clock would be used, could we still use the analog delay function?

Thanks

Best regards

Mia