Tool/software:

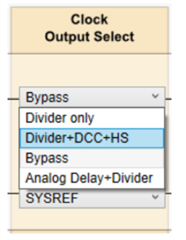

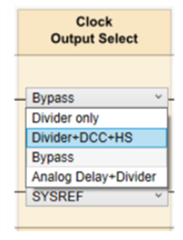

LMK04828: DCLK :144MHz SYNC PIN :9MHz Under the condition, sdclk(sysref) duty cycle is not 50%. In the sdclk(sysref) output port Some output ports satisfy 50%, but othersdclk(sysref) output ports are around 56%.

I'm curious about the cause