Other Parts Discussed in Thread: SN65LVDT14

Hello Team,

Can you help with the question below:

Need clarification on CDCLVC1106 clock buffer’s datasheet slew rate specification. We’re planning to use this part downstream of TI’s SN65LVDT14 LVDS transceiver for a SPI clock signal that will be fanned out to 6 SPI slaves. However, the clock buffer has a spec on maximum input slew rate that appears will render it incompatible with the LVDS transceiver’s minimum output rise/fall times with a 3.3-V supply.

LVDS Transceiver:

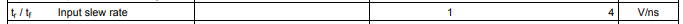

Clock Buffer:

We haven’t seen a spec for maximum input slew rate on a buffer like this before, so we’re wondering what the risk and potential failure mode may be if we exceed the maximum. Could you let us know if using these parts together would be problematic?