Hi.

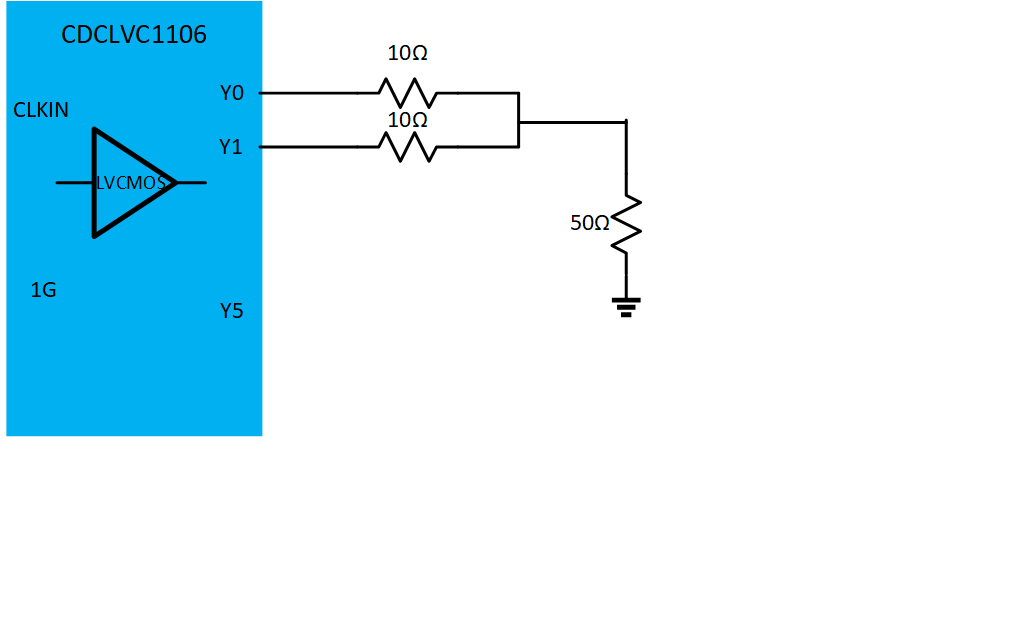

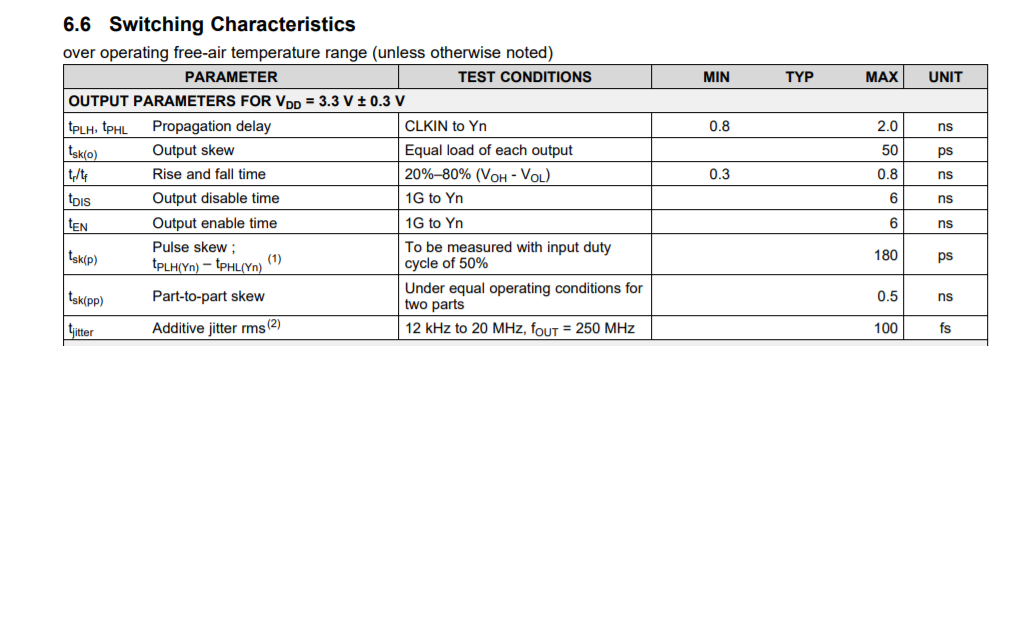

I am using a CDCLVC1106 in an application where I need to distribute a precision 10MHz square wave clock to several pieces of lab equipment. On most of the equipment the receive side is 50-ohm terminated (as is good transmission line practice) and this 50 ohm termination is not removable. When I use the CDCL1106 to send this signal it has insufficient drive current to give me the needed 3.3 volt swing to trigger the logic of some of the lab equipment. I found that if I tie the output of two channels of the '1106 together, (each with a 10 ohm buffer resistor) I get enough drive to run the lab equipment. My question is, is this an OK thing to do? Personally I see no difference of paralleling two output channels to that of having each channel drive its own load, but I am asking the experts. Will this affect the pin-to-pin skew? Will this affect the jitter? Better question may be, what part (if any) do you recommend for driving CMOS levels through transmission lines that are 50 ohm terminated?

Thank you,

---Lou