Other Parts Discussed in Thread: CDCLVP1204

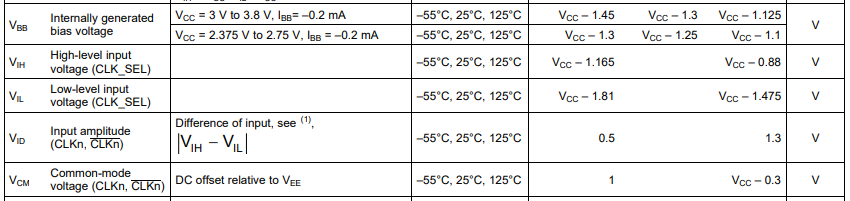

Using the CDCLVP111-SP clock buffer with a 3.3V LVCMOS single-ended input, following interface described in Figure 8 of the data sheet. It works fine, but there is a concern that the clock input signal levels do not meet the spec requirements listed in section 6.6 for Vcc = 3.3V, VEE = 0V, Particularly Vid.

Also, not sure what Vih/Vil specs refer to as they call out CLK_SEL which should be LVTTL/LVCMOS compatible. For example with Vcc = 3.3V, Vih limits are 2.135V min, 2.42V max. Does this mean CLK_SEL level needs to be between these values, or that this is the min and max of the threshold voltage?

Does this mean the Clock needs to be attenuated? I noticed that some CDCLVP clock buffers (like CDCLVP1204) had separate specs for LCMOS input as a single-ended input.

Input frequency is 60 MHz in this application