Other Parts Discussed in Thread: CDCE62005, DAC3174

Hello, I'm Lee.

I have been using a TSW1400EVM as DAC pattern generator with DAC3171EVM for 1 week.

Now, I have some questions about this system.

First, Does DAC3171EVM need an external clock signal over 500MHz?

In my desk, there only are two function generator 20MHz, 100MHz.

And, should I enter number of Sampling Per Second(SPS) less than clcok freq. ?

I have tested various numbers, such as 1G, 100M, 100k, 1k,and so on,

but there were not any change in output waveform.

(additional) Is there any recommended product with clock signal?

Second, Why my output waveform has less power and different freq. from desired form?

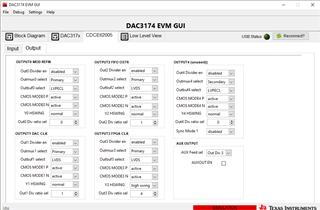

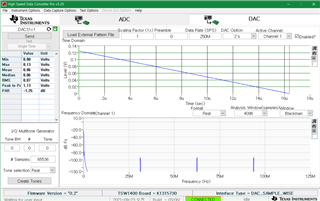

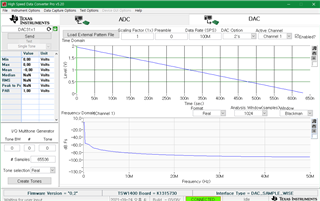

I downloaded Highspeed Data Converter pro and DAC3174GUI in your website,

and I send .reg file that is provided with GUI to DAC3171EVM.

I loaded external pattern file, and this was desired waveform.

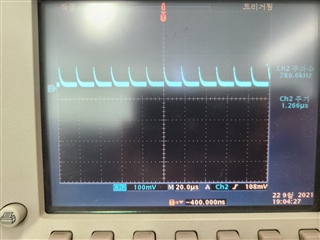

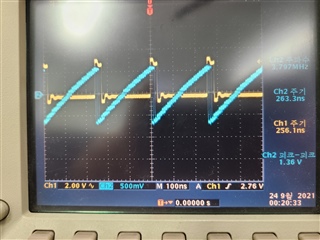

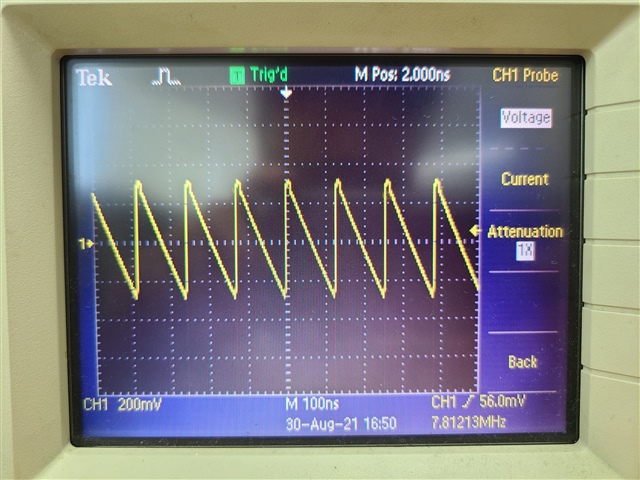

However, the output waveform was this.

I wished to make a waveform like sawtooth, but the output was reversed and had different freq, max/min voltage.

Why these happen? Is this relative with insufficient clock?

If helpful, I uploaded the external pattern file, dpg1.txt

Please, help me. Thank you.

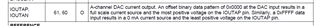

0 0 1000 1000 2000 2000 3000 3000 4000 4000 5000 5000 6000 6000 7000 7000 8000 8000 9000 9000 10000 10000 11000 11000 12000 12000 13000 13000 14000 14000 15000 15000 16000 16000 17000 17000 18000 18000 19000 19000 20000 20000 21000 21000 22000 22000 23000 23000 24000 24000 25000 25000 26000 26000 27000 27000 28000 28000 29000 29000 30000 30000 31000 31000