Other Parts Discussed in Thread: DAC34H84, , DAC3484, LMK04828, CDCE62005

Hello,

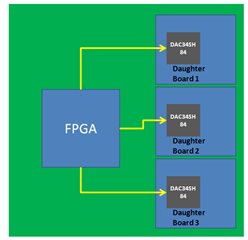

We plan on having multiple FMC boards each having one DAC34SH84 on a single carrier board with FPGAs. The instantaneous bandwidth of the system is 500MHz. Is it realizable with the DAC34SH84 and the DAC34H84?

2) How do we synchronize the devices on different boards (there is a mention of OSTR for sync) but physically how do we connect them to the different FMC boards.

3) DACCLK and OSTR are differential signals, do we connect multiple (4 coaxial/SMA cables) to each of these boards?

4) Can we put the clock generation chip on the carrier board and then route them to the DAC ICs through the FMC connectors?

5) Any reference design for interfacing FPGA (Xilinx) to these DACs?

6) The DACs have to generate zero IF I and Q to feed IQ modulators that have single ended inputs. Please advise on suitable circuitry? IQ imbalance correction and LO leakage correction have to be performed as well. Since the ICs already have this feature how will we make use of them if lets say an opamp (transformer is ruled out since the output is zero IF) is used to convert the differential to single ended signals. Do we add some sort of bias-t at the opamp output to introduce the dc for cancelling LO leakage?

Thanks for your help,