Hello,

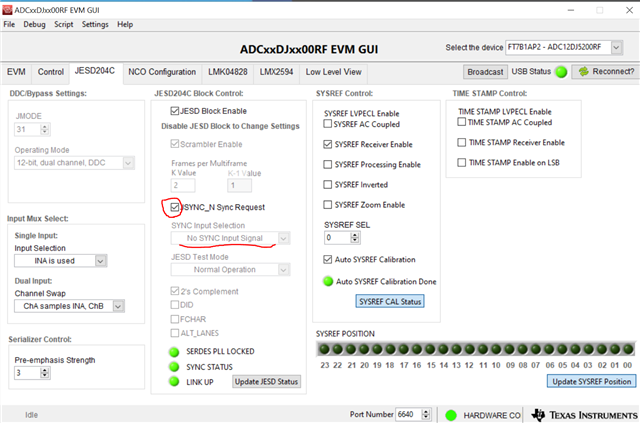

ADCxxDJxx00RF EVM GUI, I can see SERDES PLL Locked LED is green.

This PLL status follows the ADC sampling clock from the external RF signal generator.

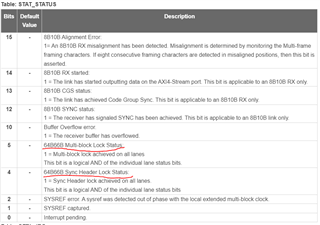

But SYNC STATUS and LINK UP LEDs are dark green.

This status means I can't read SerDES output data.

How to debug the point to make ADC LINK UP?

My setup is as follows:

JMODE 31

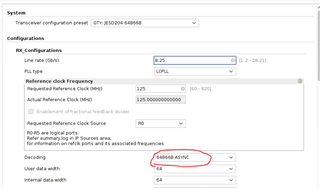

FPGA reference 125 MHz

External Fs 2500 MHz

SerDES rate 8250 MHz

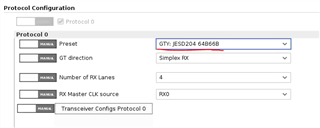

At the FPGA side:

Core clock 124.751 MHz

GTY rx user clock 124.751 MHz

Sysref 3.906281 MHz

FPGA GTY IBERT measurement 7.997 Gbps

Thanks,

Kiman