Hello,

My customer has an issue that the DAC37J82 they designed have no output.

They are using the DAC37J82 with the following conditions.

- DAC Data Rate input : 245.76Mhz

- Lane : 4 (LMF = 421)

- Interpolation : 2

- DAC Output rate : 491.52Mhz (DAC CLK 491.52Mhz)

- FPGA JESD CLK : 245.76Mhz

- JESD Line rate setting value: 2.4576Ghz

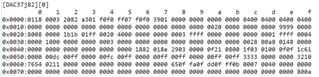

- Register settings

Here's what they checked:

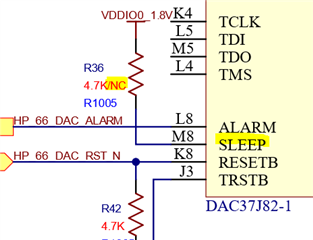

- TX_Enable = 1 & ResetB = 1

- SysRef P/N input (jesd_core clk / 64, 0.96MHz), Alarm 00

- DAC_SYNC output high (DAC -> FPGA sync signal is high)

- FPGA -> DAC signal (EYE Diagram)

- Serdes PLL Locked

- 4 Lane alignment Alarm OK (0x64/0x65/0x66/0x67 : 0000).

1. What else should they check to fix the DAC37J82 no output issue?

2. They are using only A and D of IOUTx. unused B and C are floating. Could the problem of not connecting the unused IOUT to GND have something to do with the no output?

Thank you.

JH