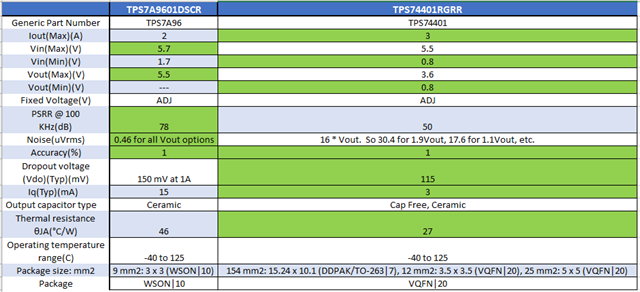

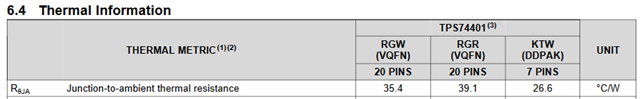

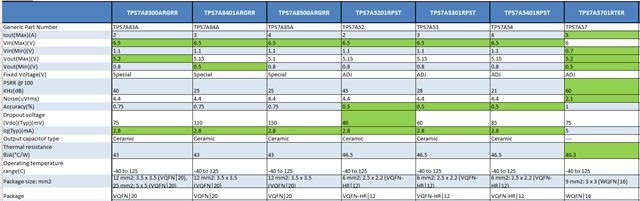

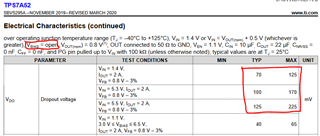

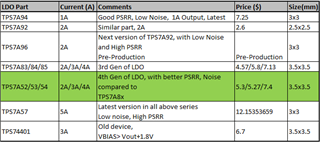

Other Parts Discussed in Thread: TPS62913, , TPS7A94, TPS7A92, TPS7A96, TPS74401, TPS7A84A, TPS7A52, TPS7A57, TPS7A54

Hi Team,

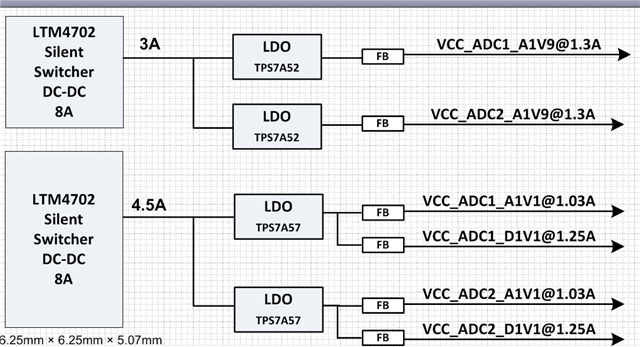

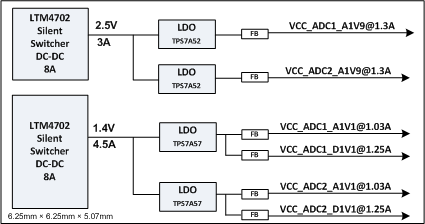

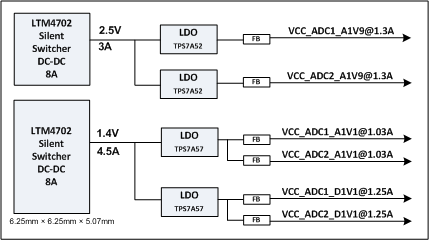

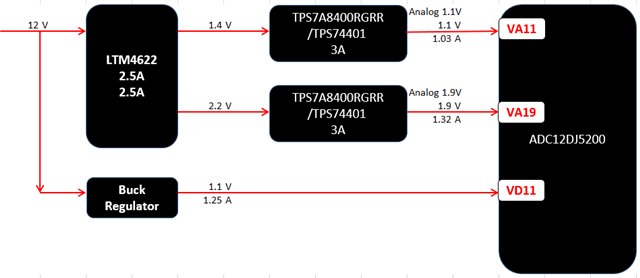

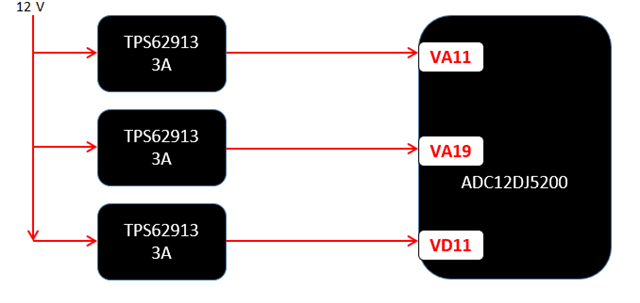

We are using 2 ADC12DJ5200 for 4 Channel

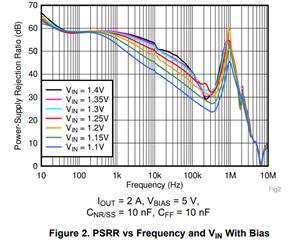

I've few questions on power supply regulator + LDO vs Silent switch TPS62913

Case1: Using Regulator + LDO,

Q1: Can the Digital 1.1V (VD11) Supply be directly sourced from Switching regulator or Should be from LDO?

Case2: Using Silent Switcher: TPS62913

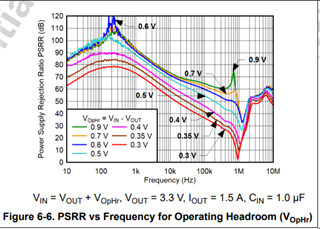

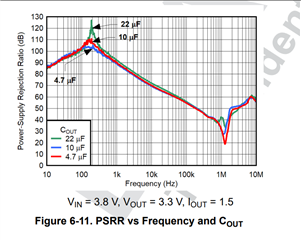

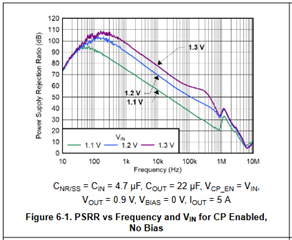

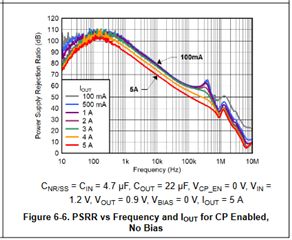

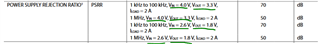

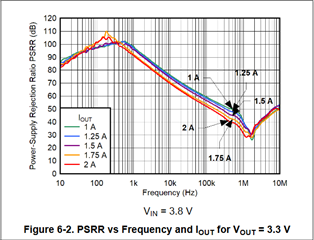

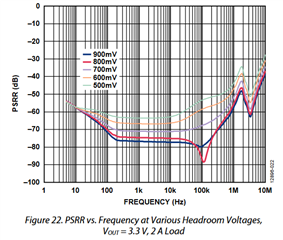

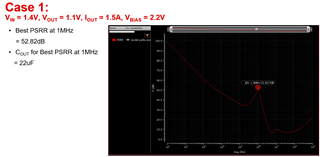

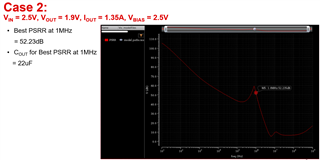

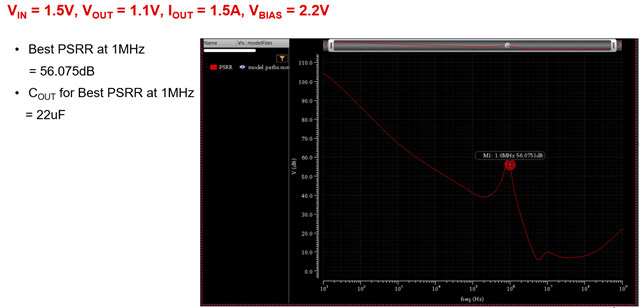

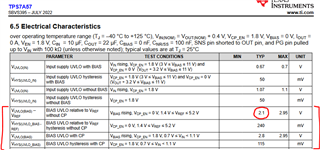

Q2: For the silent switcher IC, Can you please share the PSRR values?

Q3: Which one do you suggest over Case1 vs Case2?

Q4: Related SPI Signals of ADC12DJ5200, Control signals are referenced to 1.9V(max), Can I directly connect the SPI signals to controller (Xilinx FPGA) 1.8 Level support? Or recommends level translator?

Thanks.