Other Parts Discussed in Thread: LMK04808

Hello,

My customer received support as below link for DAC37J82 no output issue.

The previous thread is locked, so we open a new one here.

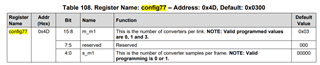

While debugging, they found that CH A output came out when the m_m1 value of Config77 was changed from 0x1 (2 converters) to 0x3 (4 converters).

Q1) Is it correct to set the m_m1 value of Config77 to 0x3 (4 converters) to use Dual Channel (CH A / CH D only)?

Q2) Unlike CHA, CH D still has no output. Please review if there is a problem with the register settings below.

[DAC37j82] setting

0 1 2 3 4 5 6 7 8 9 A B C D E F

0x0000: 0018 0803 2082 A301 F0F0 FF07 F0F0 2502 0000 0000 0000 0000 0400 0400 0400 0400

0x0010: 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0026 0000 0000 0000 9999 0000

0x0020: 8008 0000 1B39 01FF 0020 2000 0000 0000 0003 FFFF 0000 0000 0000 0001 FFFF 0004

0x0030: 0000 1000 0000 0000 0003 0000 0000 0000 0000 0000 0000 0800 0028 0088 0108 0000

0x0040: 0000 0000 0000 0000 0000 0000 0044 190A 31C3 0000 0F01 0801 1F03 0300 0F0F 1C61

0x0050: 0000 00DC 00FF 0000 00FC 00FF 0000 00FF 00FF 0000 00FF 00FF 0000 0000 0000 0123

0x0060: 4567 0211 0000 0000 0000 0000 0000 0000 440A B70B 7A07 6F02 0007 00F0 0000 0000

0x0070: 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 800A

Thank you.

JH