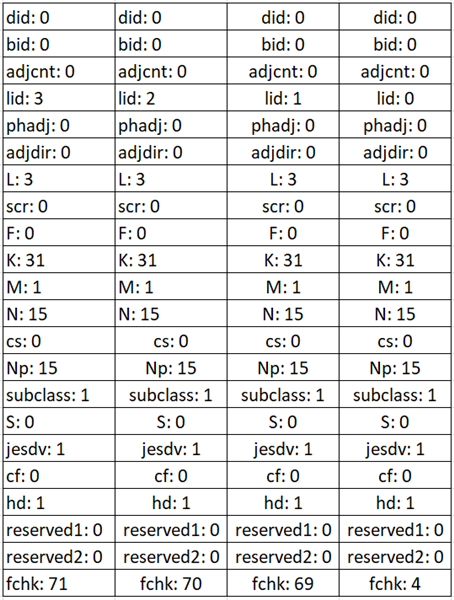

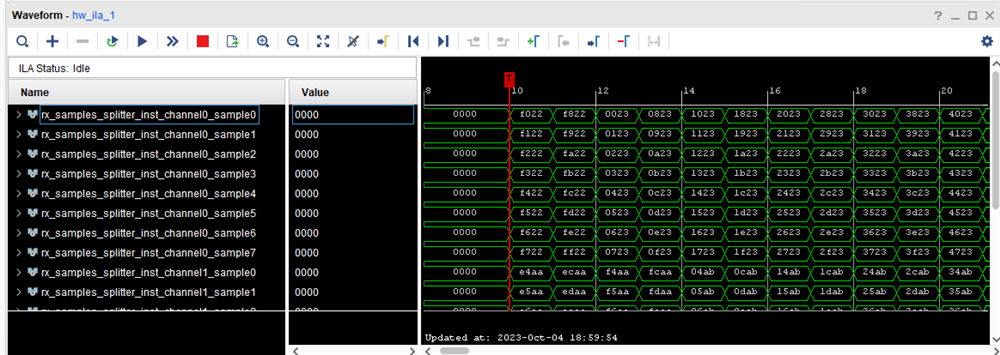

Following table 18 divide by 6, when attempting to use the ADC with an LMFS setting of 4211 we are getting an output that matches what we would expect with 4244. When setting LMFS we also get the behavior of 4244. This is present both when using the ramp test pattern in the DDC block and in normal oepration.

ADC Reg Dump:

Master Page Regs:

0x20: 0x0000

0x32: 0x0000

0x39: 0x0050

0x3c: 0x0000

0x3d: 0x0005

0x57: 0x0010

0x58: 0x0000

0x5a: 0x0000

ADC Page Regs:

0x3f: 0x0000

0x42: 0x0003

Offset Correction Page Regs: (Channel A Channel B)

0x68: 0x0042 0x0042

Digital Gain Page Regs: (Channel A Channel B)

0xa6: 0x0000 0x0000

Main Digital Page Regs: (Channel A Channel B)

0x00: 0x0000 0x0000

0xa2: 0x0008 0x0008

JESD Digital Page Regs: (Channel A Channel B)

0x01: 0x0080 0x0080

0x02: 0x0000 0x0000

0x03: 0x0002 0x0002

0x04: 0x0000 0x0000

0x06: 0x0000 0x0000

0x07: 0x001f 0x001f

0x16: 0x0070 0x0070

0x17: 0x0000 0x0000

0x32: 0x0000 0x0000

0x33: 0x0000 0x0000

0x34: 0x0000 0x0000

0x35: 0x0000 0x0000

0x36: 0x0040 0x0000

0x37: 0x0002 0x0002

0x3c: 0x0001 0x0000

0x3e: 0x0060 0x0060

Decimation Filter Page Regs: (Channel A Channel B)

0x00: 0x0001 0x0001

0x01: 0x0001 0x0001

0x02: 0x0000 0x0000

0x05: 0x0001 0x0001

0x06: 0x0000 0x0000

0x07: 0x0000 0x0000

0x08: 0x0000 0x0000

0x09: 0x0000 0x0000

0x0a: 0x0000 0x0000

0x0b: 0x0000 0x0000

0x0c: 0x0000 0x0000

0x0d: 0x0000 0x0000

0x0e: 0x0000 0x0000

0x0f: 0x0000 0x0000

0x10: 0x0000 0x0000

0x11: 0x0000 0x0000

0x14: 0x0000 0x0000

0x16: 0x0000 0x0000

0x1e: 0x0041 0x0041

0x1f: 0x0001 0x0001

0x33: 0x0000 0x0000

0x34: 0x0000 0x0000

0x35: 0x0000 0x0000

0x36: 0x0000 0x0000

0x37: 0x0004 0x0004

0x3a: 0x0000 0x0000

Power Detector Page Regs: (Channel A Channel B)

0x00: 0x0000 0x0000

0x01: 0x0010 0x0010

0x02: 0x0000 0x0000

0x03: 0x0000 0x0000

0x07: 0x00e6 0x00e6

0x08: 0x00cc 0x00cc

0x09: 0x00b3 0x00b3

0x0a: 0x0099 0x0099

0x0b: 0x0000 0x0000

0x0c: 0x0000 0x0000

0x0d: 0x0000 0x0000

0x0e: 0x0000 0x0000

0x0f: 0x0000 0x0000

0x10: 0x0000 0x0000

0x11: 0x0000 0x0000

0x12: 0x0000 0x0000

0x13: 0x0000 0x0000

0x16: 0x0000 0x0000

0x17: 0x0000 0x0000

0x18: 0x0000 0x0000

0x19: 0x0000 0x0000

0x1a: 0x0000 0x0000

0x1d: 0x0000 0x0000

0x1e: 0x0000 0x0000

0x20: 0x0000 0x0000

0x21: 0x0000 0x0000

0x22: 0x0000 0x0000

0x23: 0x0000 0x0000

0x24: 0x0000 0x0000

0x25: 0x0000 0x0000

0x27: 0x0000 0x0000

0x2b: 0x0000 0x0000

0x33: 0x0005 0x0005

0x34: 0x000d 0x000d

0x35: 0x000e 0x000e

0x36: 0x000e 0x000e

0x37: 0x0000 0x0000

0x38: 0x0000 0x0000

Other notes:

Previously we were using the ADC without decimation and LMFS of 8 2 8 20. Its possible we make a mistake when converting.