Hello,

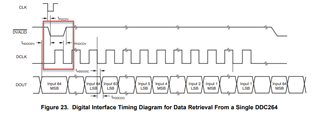

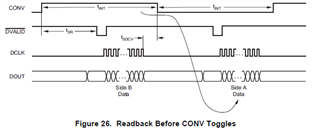

I have a question for people who have experience DDC264EVM evaluation board and its software. I'm trying to set FPGA configuration registers in the evaluation board with four DDC264 to have an integration time of 1 ms. Basically, I want to do a data retrieval before the CONV signal toggles as described in the image below:

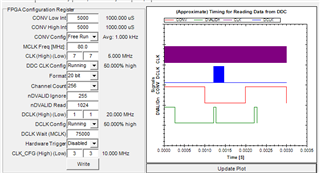

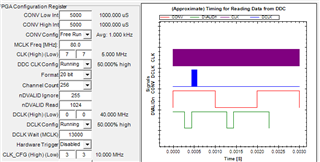

I set 20MHz DCLK, 5 MHz CLK, and CONV 5000 CLK cycles (1000 ms), but the problem is that the DVALID pulse becomes too wide when I set the DCLKWait value larger to put DCLK pulses inside CONV active low state. I would be happy if anybody knew what I'm doing wrong or had already dealt with long integration times and has proper parameters.