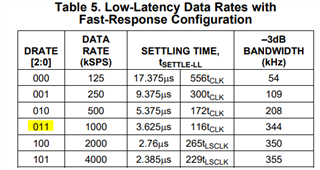

It is not clear in the datasheet but could you please confirm:

| Data Rate | Min f_clk |

| 4 MSPS | 32 Mhz |

| 2 MSPS | 16 Mhz |

| 1 MSPS | 8 Mhz |

I have configured the ADS1675 for CMOS and therefore I am limited to 1 MSPS.

I understand that that the min/max specs for the ADS1675 is for 32 Mhz, but are there any major disadvantages to using an 8 Mhz clock vs a 32 Mhz clock?