Part Number: DAC3283EVM

Other Parts Discussed in Thread: DAC3283

Hi,

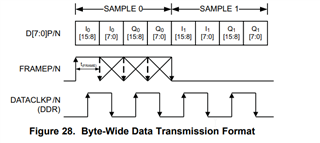

1. DAC 3283 datasheet says:

So it says that maximum Input data rate is 312.5 MSPS. Does this means that Max. DATACLK frequency can be 312.5 MHz.

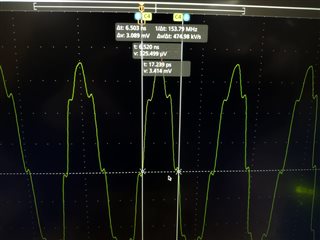

BUT test condition says that DATACLK frequency is 625MHz. So what is max. DATACLK freq? (I am assuming here that DATACLK frequency and the clock at which 8 bit data generated for DAC is same).

2. Does the DATACLK freq should be half of the DACCLK frequency?