Other Parts Discussed in Thread: LMK04828

Tool/software:

Greetings,

I am trying to use the DAC39J82EVM with a ZCU102 board and I am having quite a bit of difficulties to set it up. In particular, I requested and received the TI-JESD IP that comes with a reference design for the ZCU102, which is what I'm trying to implement. The reference top design has 4 clock signals that need connection, and the constraints file that comes with the reference design has the following pins assigned:

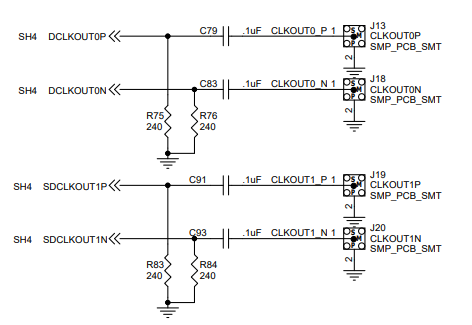

| Clock signal | Pin name | FMC Pin | DAC3XJ8XEVM schematic |

| sys_clk_p | CLK1_M2C_P | G2 | Not assigned |

| refclk_p | GBTCLK0_M2C_C_P | D4 | GTX_CLKP |

| sysref_p | LA22_P | G24 | Not assigned |

| tx_sync_n | LA26_P | D26 | Not assigned |

Now, if I understood corectly how these clocks work:

- sys_clk_p should be routed to a clock with frequency LineRate/80 (for my data_width=64). I assume that, on the DAC schematic it should be connected to FMC_DACCLK_P, so FMC pin D8. Once I know the linerate I understand I need to modify the clocking wizard present in the reference design to match the frequency of this clock and the wanted generated clocks.

- refclk_p I think is routed correctly to GTX_CLKP

- sysref_p I understand should be conected to FMC_SYSREF_P, which corresponds to FMC pin D11

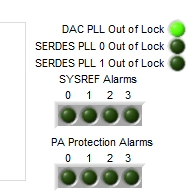

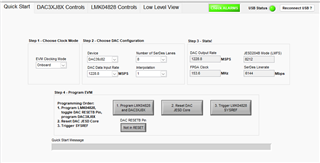

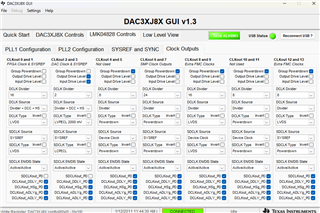

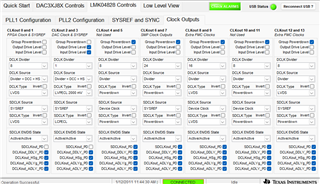

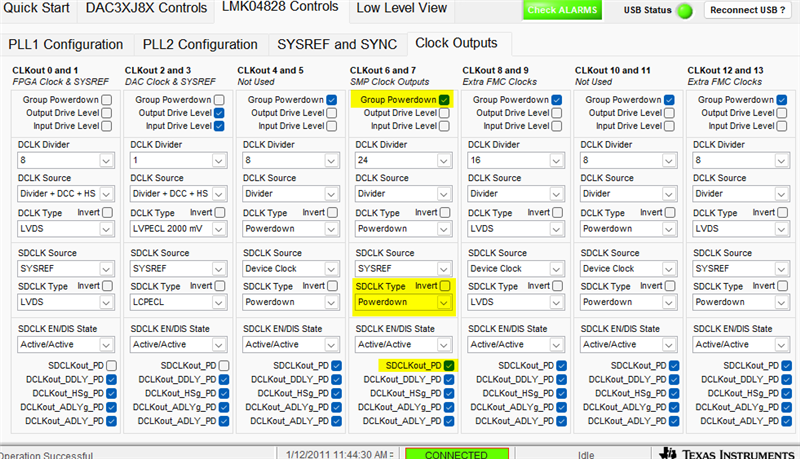

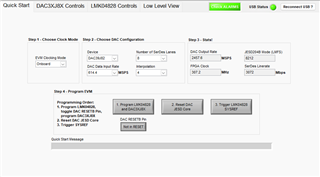

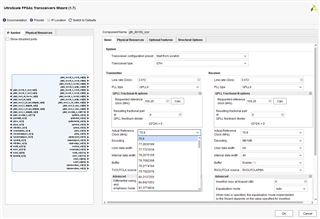

With this in mind I set the GUI with the following parameters

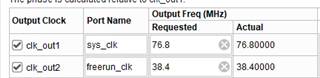

Which would mean that the sys_clk clock should have a frequnecy of 38.4 MHz, so I set that as the input frequency in the clocking wizard. Moreover, when I set the parameters in the Transceiver Wizard the minimum frequency I can set is 76.8 MHz instead of 38.4 MHz for the Actual Reference Clock, which I assume corresponds to the sys_clk generated with the clocking wizard from the sys_clk_p(n) pair coming from the DAC board.

On the other hand, on the Physical Resources tab, the free-running clock frequency is set as a mximum of 38.4 MHz, and I assume this should match the frequency set to the freerun_clk output of the clocking wizard. With these two values, I set sys_clk frequency to 76.8 and freerun_clk to 38.4 in the Clocking Wizard.

I added 2 debug signals for sys_clk and sysref to be taken out some PMOD in the ZCU102, and with the configuration I mentioned I see only noise. If I try modifying the pins to what I assumed are the correct ones, Vivado throws me an error [Place 30-681] for sub-optimal placement of the clock-capable pin and MMCM pair. Any idea on this?

Thanks,

Matías.