Tool/software:

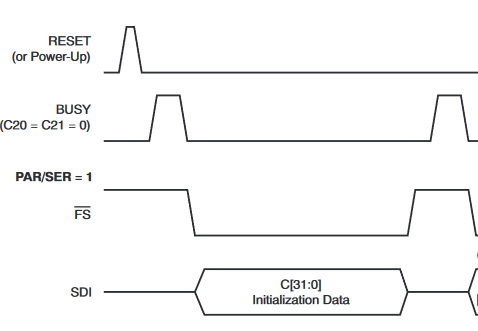

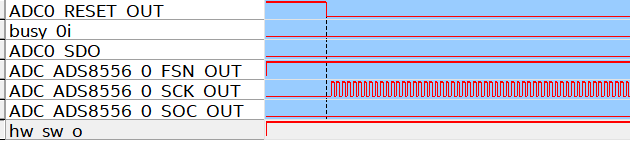

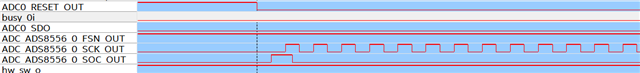

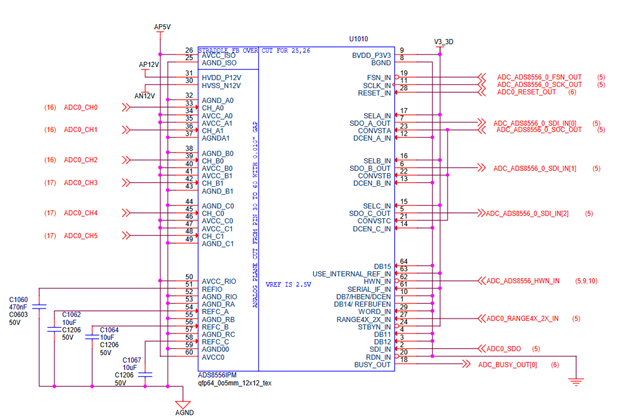

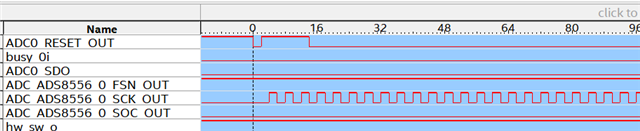

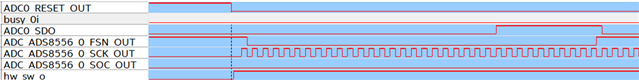

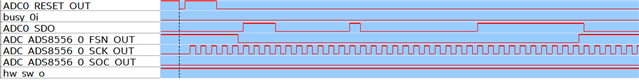

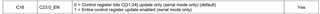

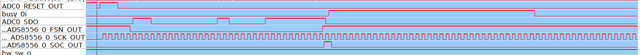

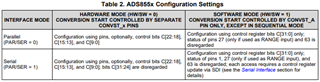

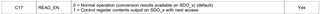

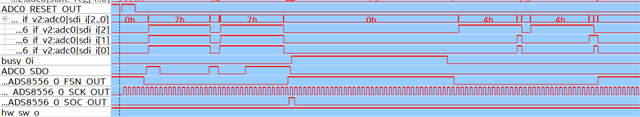

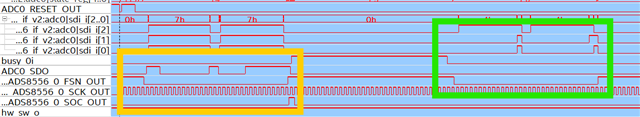

I have a ADC connected into my circuit in serial mode, completely powered up. When hardware mode is active, I get valid responses and communication from ADC. When I drive the HW_SW pin high form software mode, I do not receive the initial pulse on the busy signal from the ADC, nor do I receive a pulse on busy after deasserting and asserting the FS after the 32 clock cycles of SCLK. I'm following the exact sequence shown below but never get a response from busy.