Other Parts Discussed in Thread: LMK04828,

Hi,

I am doing almost same test with ZCU106 board + TSW14J10(rev C) + ADC31JB68EVM(rev B).

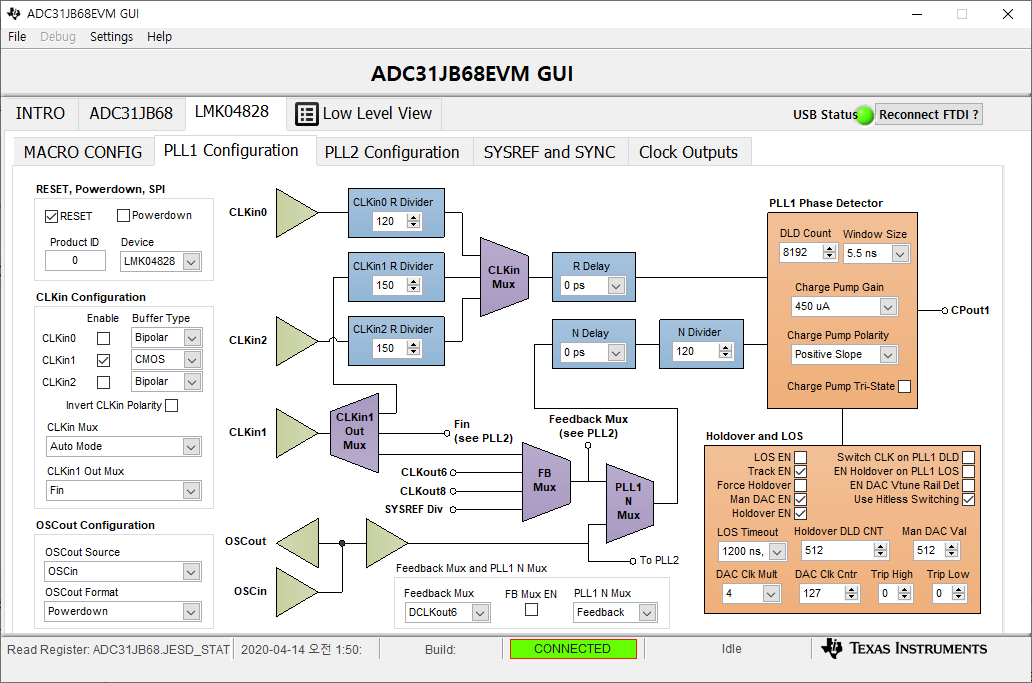

I am using Agilent N5181A signal generator's 500MHz +12dBm output for CLK input.

I had reworked two registers((R44-R45 to R51-R61) to use LMK_ADC_SYSREF(SDCLKout3).

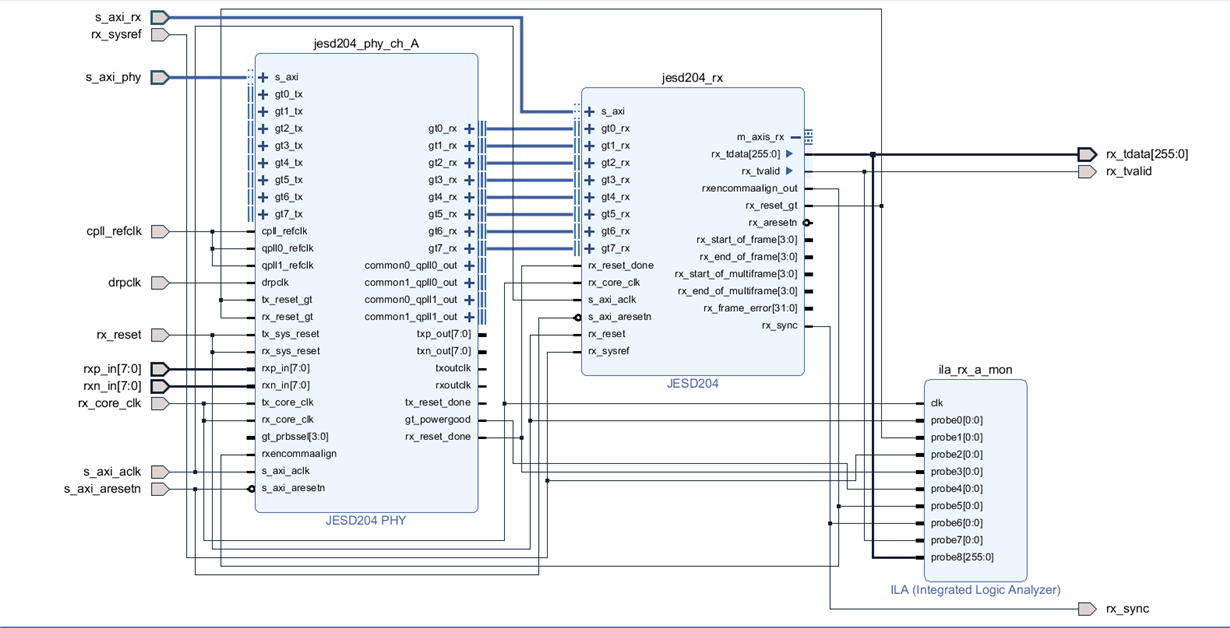

I have modified designs and firmware also, for Vivado 2019.2 & VItis.

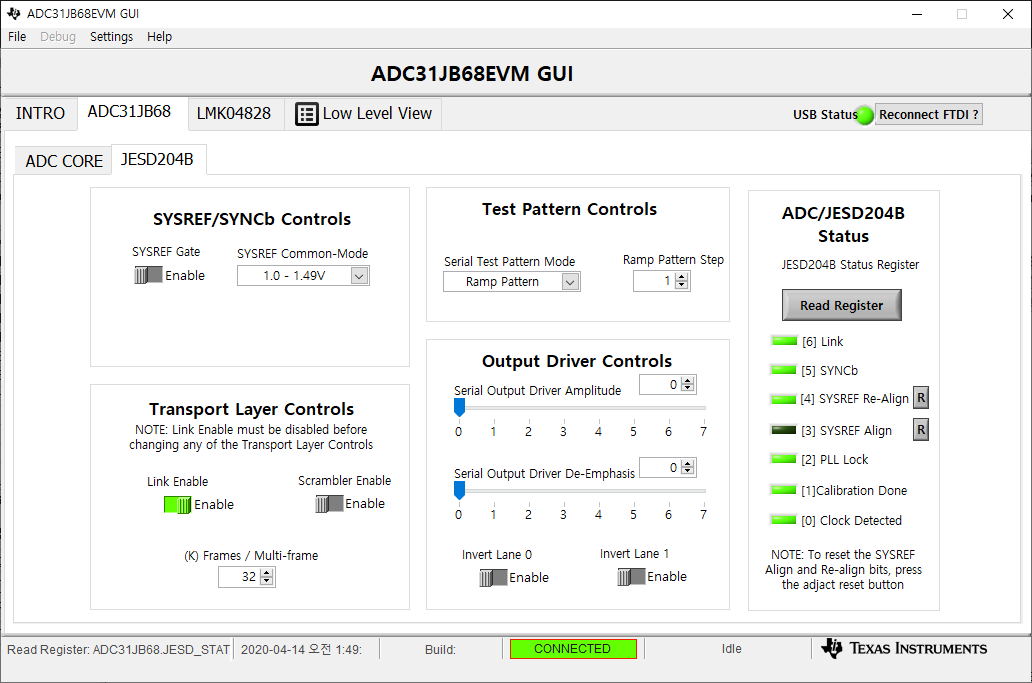

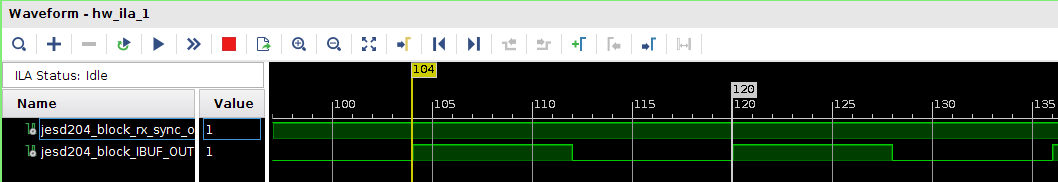

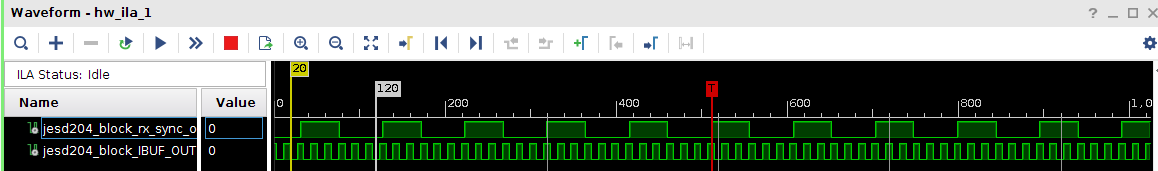

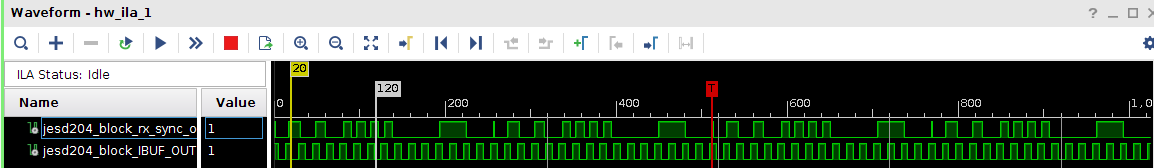

But, the link is very unstable and hard to link.

I can get JESD204b linked after tens of reset try.

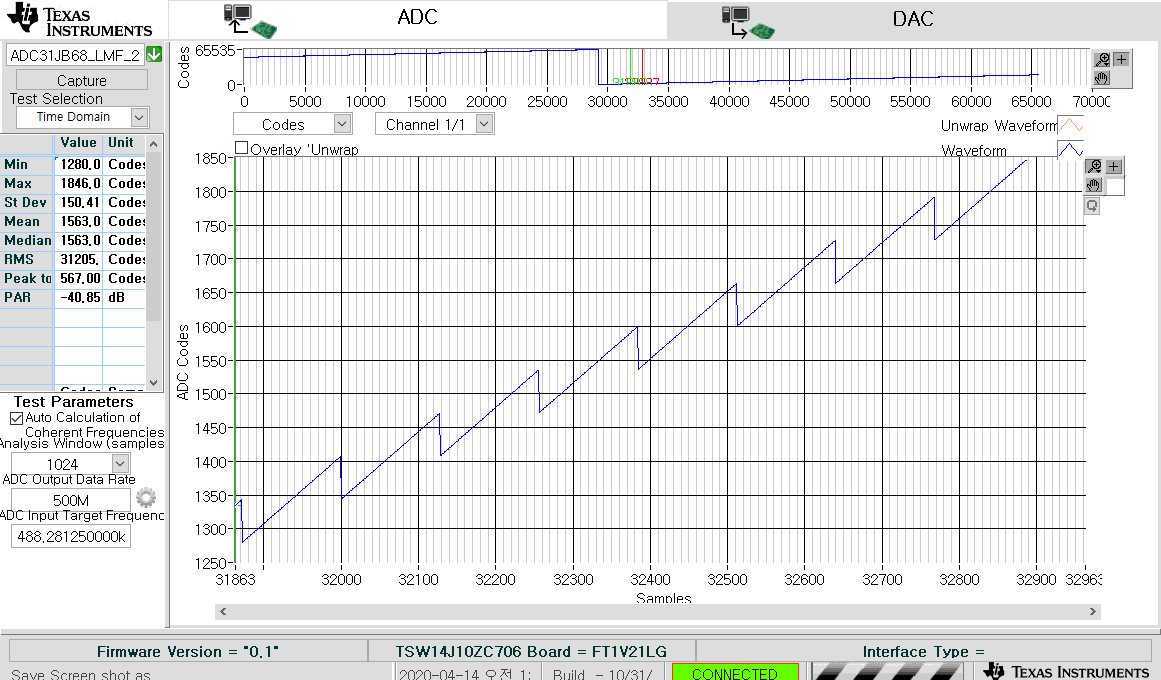

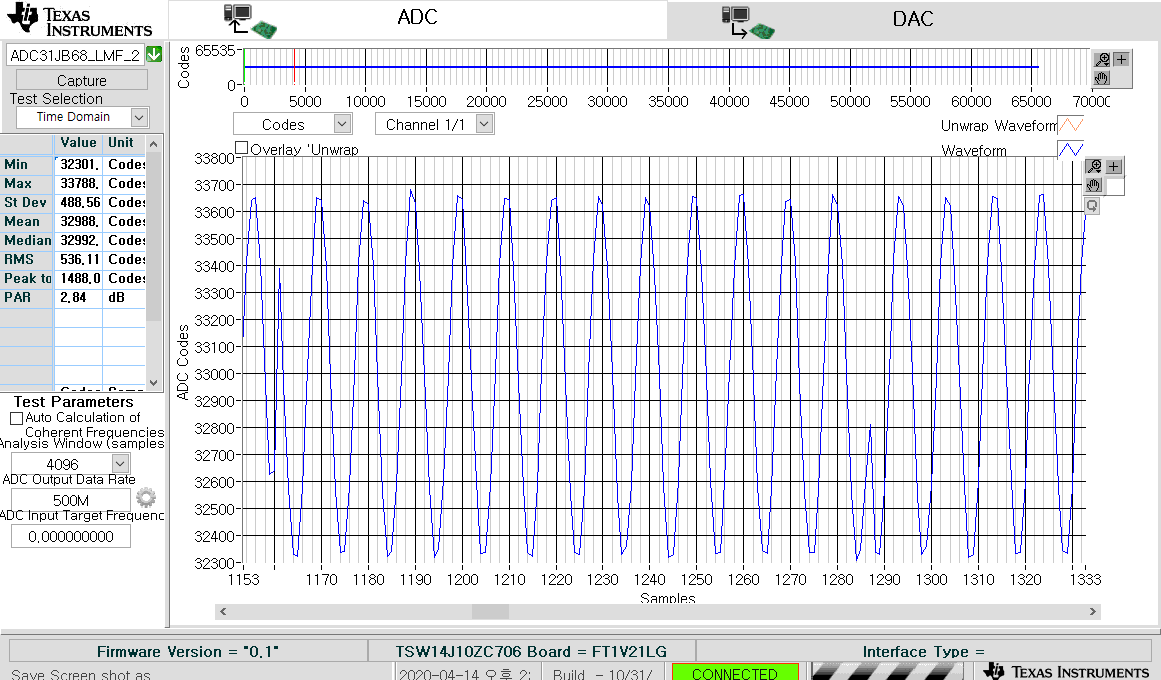

I got below ramp pattern. Is this correct pattern?

I had exported the raw data as csv file and attached it.

In every 128 samples interval. decrease as -63.

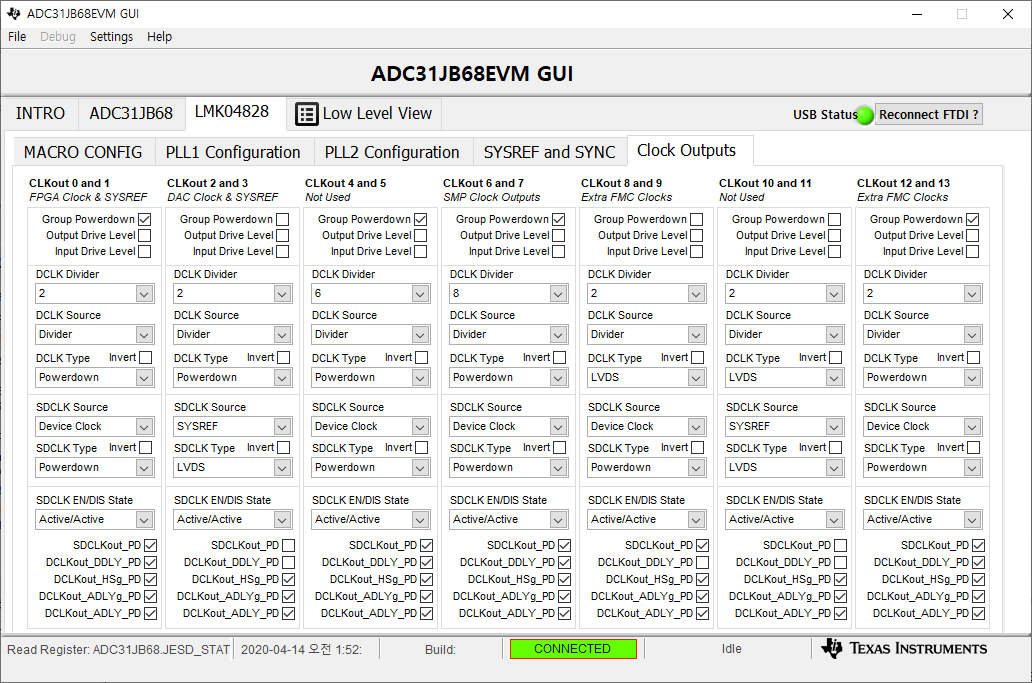

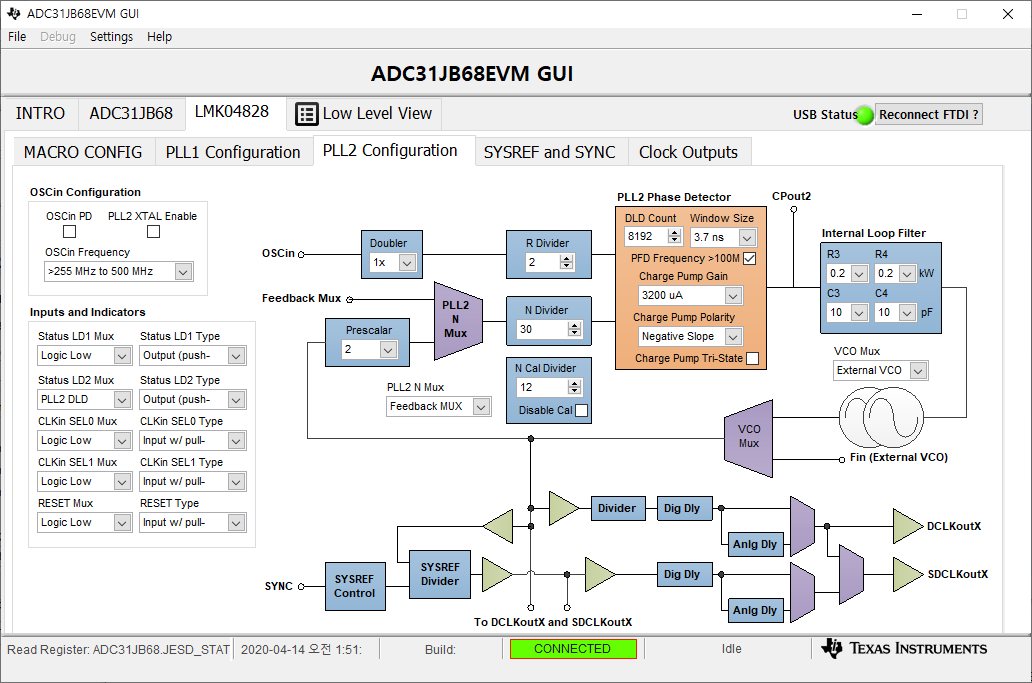

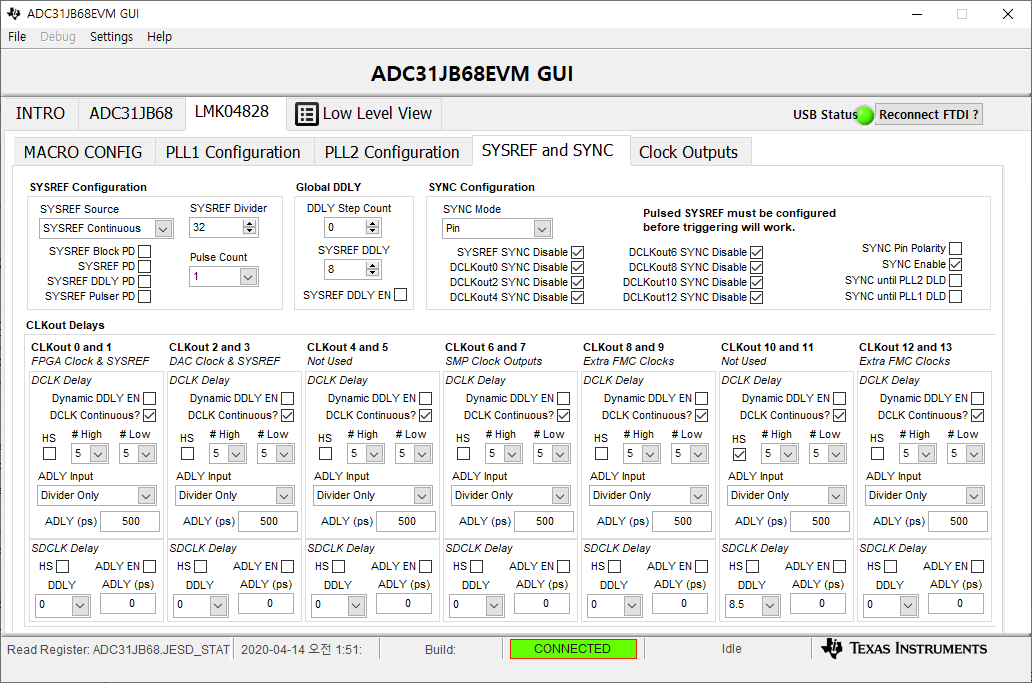

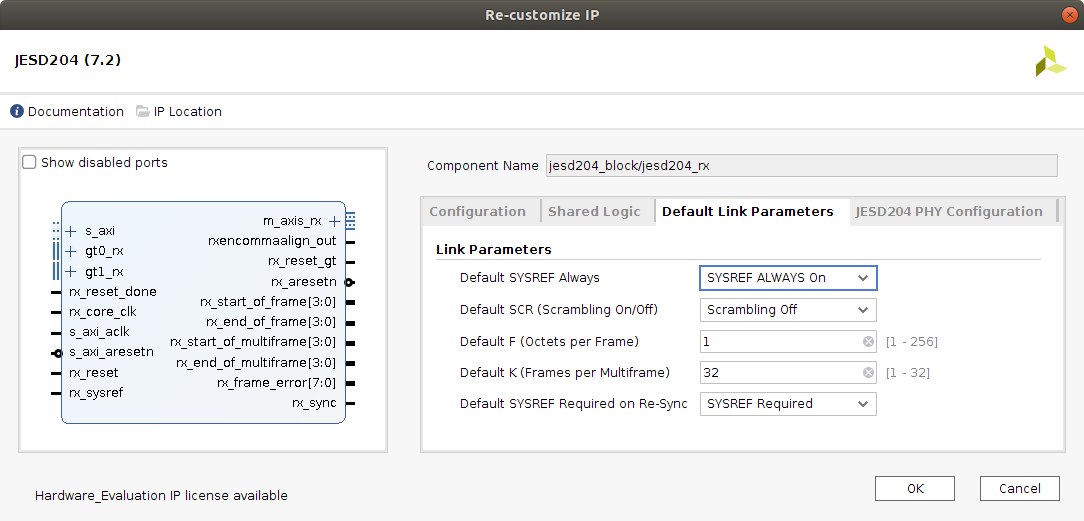

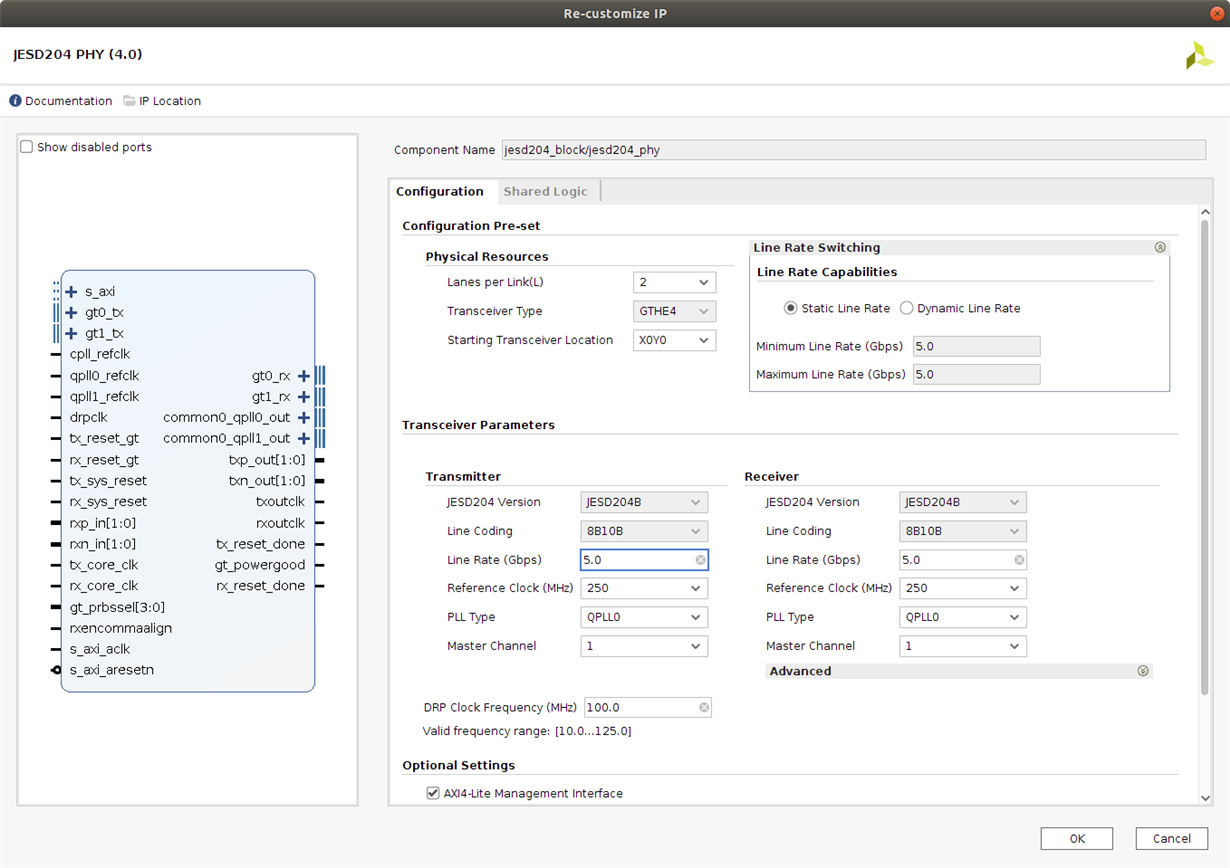

Below is GUI settings.