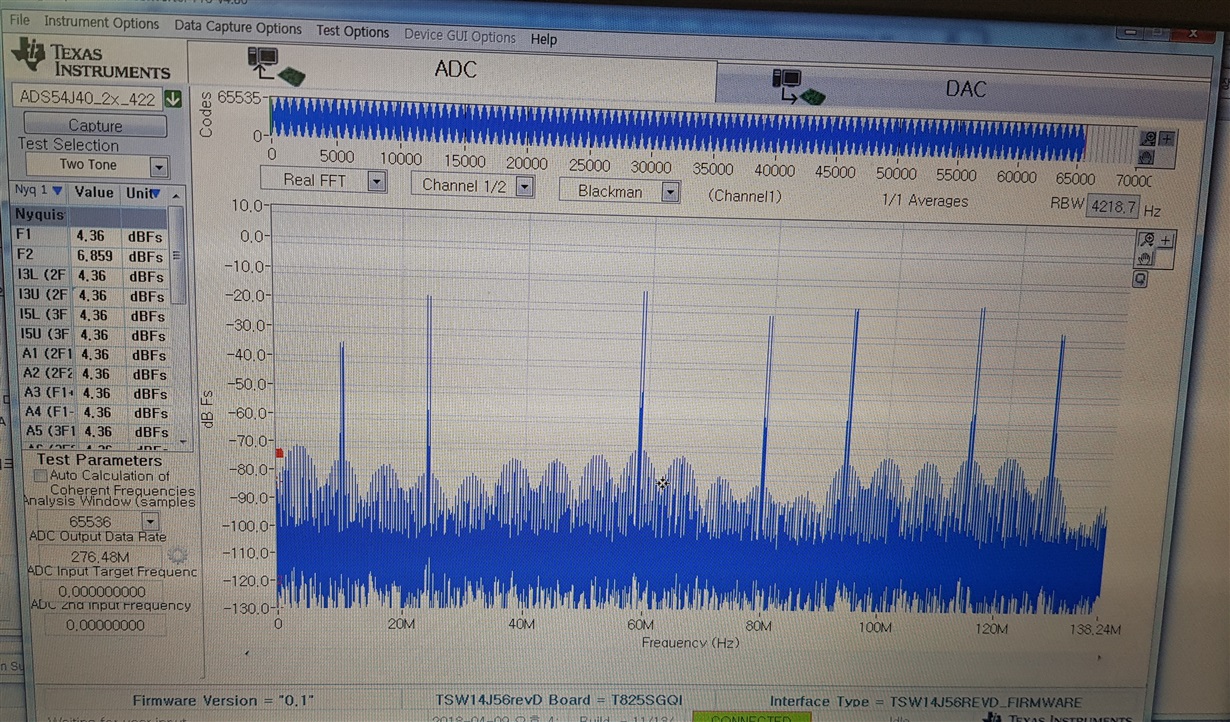

Other Parts Discussed in Thread: DAC3482, , ADS54J40

Dears.

We are developing ADS54J42.

We have an ADS54J42 problem on the board.

Band Width : 60Mhz,

LMFS=2242

Decimation : 2

Lane Rate : 5.5Gbps

We need help and solutions.

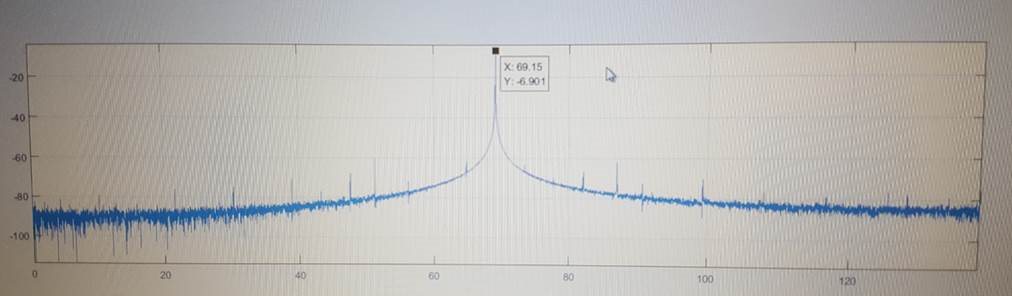

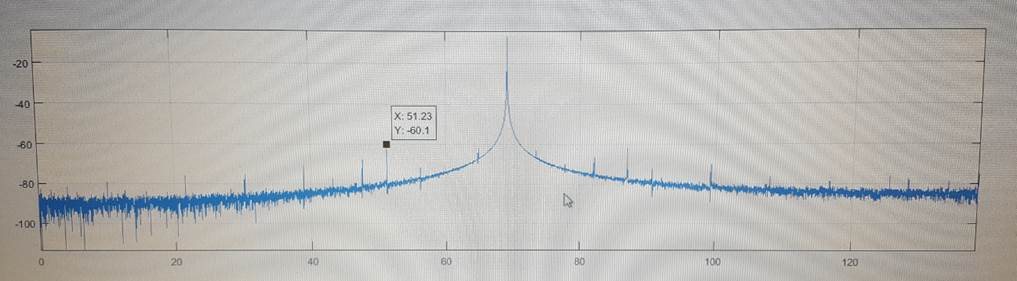

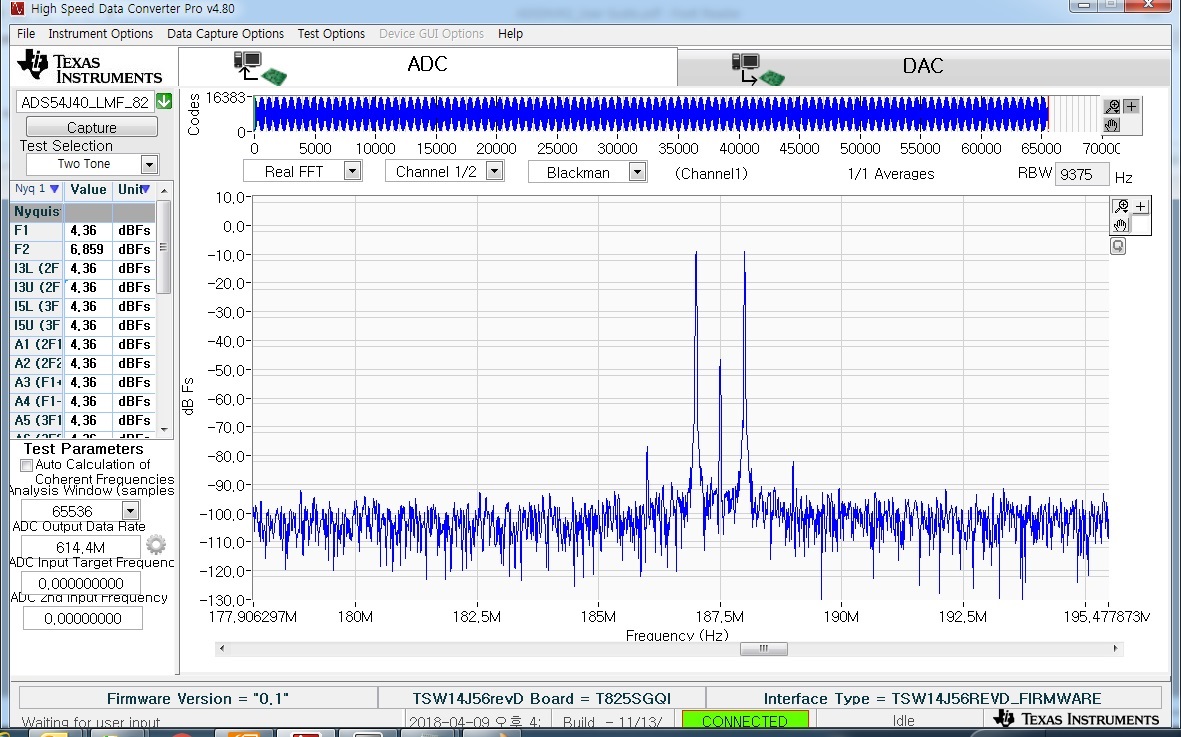

The figure below shows the ADS54J42 ADC input with matlab captured by FPGA.

The ADC clock is 276.48MHz and the IF is 207.36MHz Center.

The difference (-6.9) - (-60.1) = 53.2 is about 18MHz from the center when singleton is input.

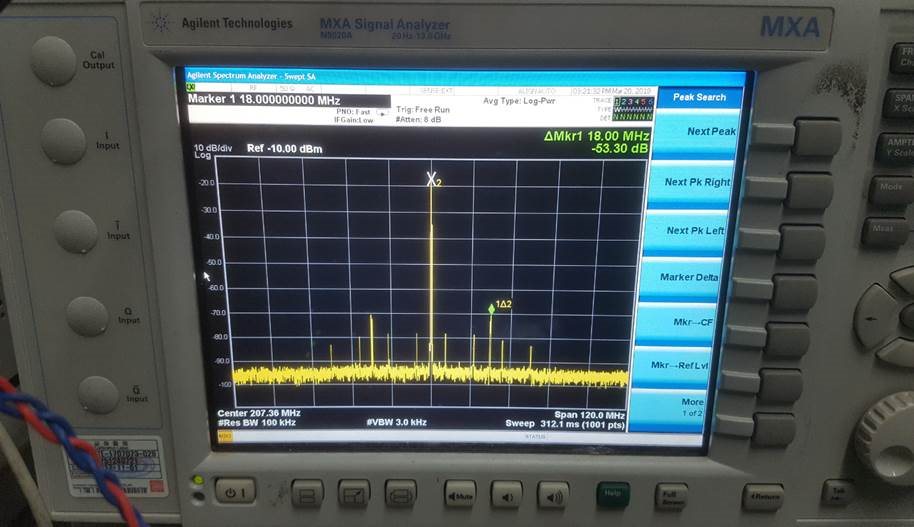

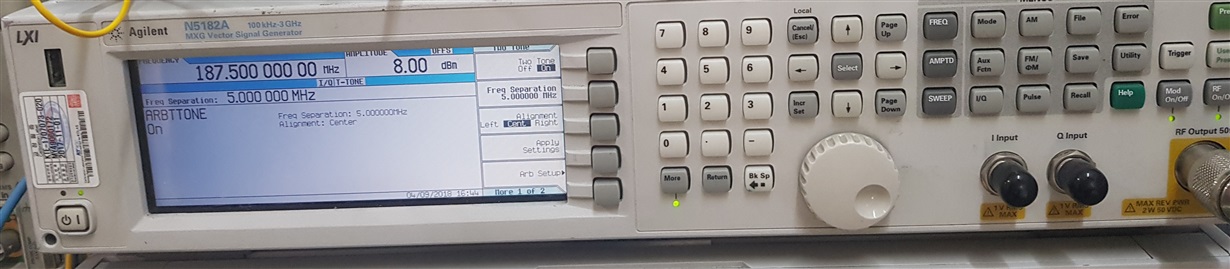

The figure below shows the ADS54J42 input looped to the DAC3482 and measured using the MXA.

At 18MHz from the center, the difference is 53.3.

The data sheet(14page) is about 70.

What's the problem?

Problems with ADS54J42 configuration?

Thank you.