Other Parts Discussed in Thread: LMK04828, ,

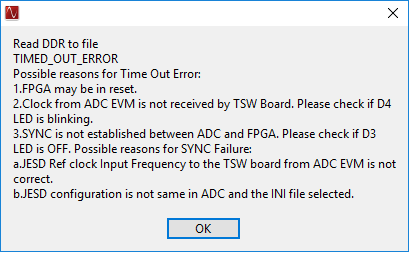

I've got a custom ADS54J66 circuit - based entirely on the EVM module - that I'm having trouble getting to sync with the TSW14J56EVM. I'm using the LMK04828 as my clock source, so everything is theoretically set up the same as the EVM. I've compared all of my clocks and register settings and everything looks good. However, I can't get the TSW EVM to sync with my board. Comparing between the ADS54J66EVM and the custom board, the one biggest obvious difference is that I'm not receiving a sync signal from the FPGA when I click the capture button.

D3 is still lit and D4 is not blinking, but I don't know what order things are supposed to happen, so I'm not sure where to start looking.

As an aside, I have a DAC module that has the same LMK part on it and I'm able to sync that to the TSW EVM, so I THINK my clocks are fine (visually, they're almost identical to the ADS54 EVM).

What prompts the TSW EVM to send the sync pulse? Is there an intermediate step that I should be doing at the register level that will signal the FPGA that I'm "ready to sync"? I think I've compared all of my signals and registers, so I'm not sure what additional steps to take.

I did change some of my lane assignments... Lane A is connected to FPGA Lane D, for instance. I thought that would just affect which channels I was seeing in the GUI... would that be a problem with the sync?

Thanks in advance.