Hi,

After change the resolution to 960x540@240hz, I've found another weird problem.

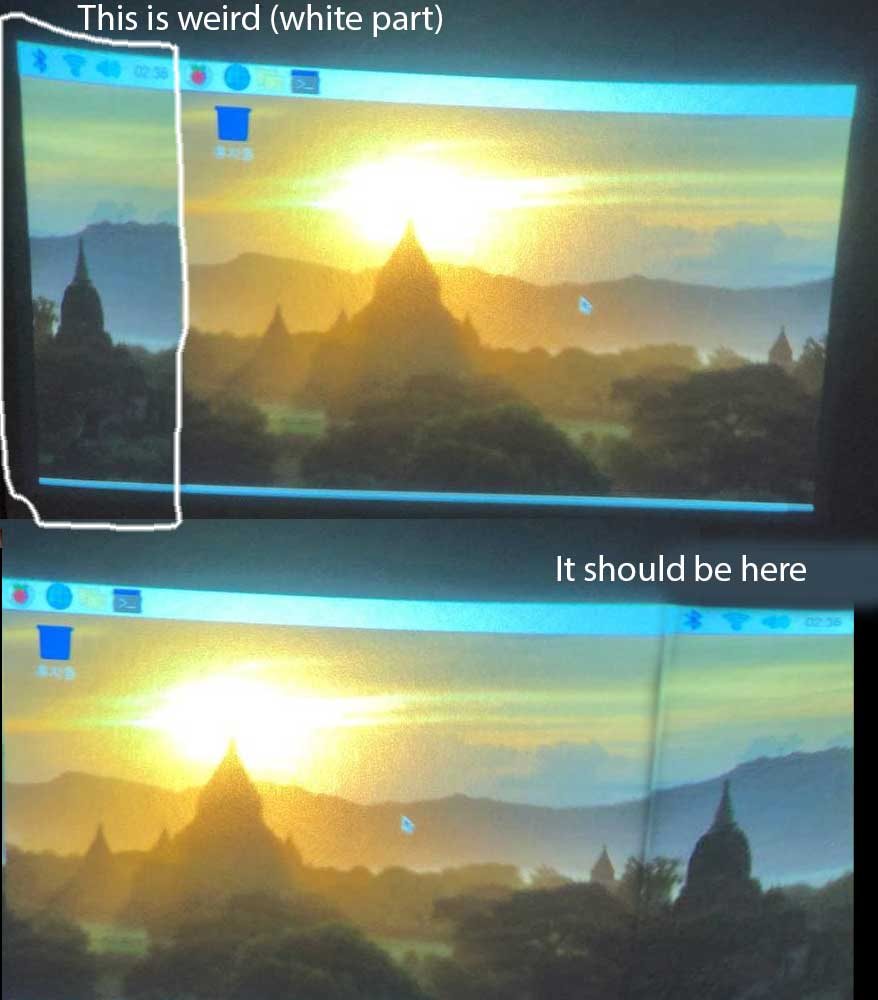

The right most part of the image is projected on the left side of the left most part.

For example, in the below image, the Raspberry icon should be the left most one.

However, as we can see the right part(e.g. timer, etc) of the image is wrapped to the left.

(due to that, we can see the vertical line in the below image)

What can be the cause of the issue?