Dear members

I am in charge of HW , and I am checking LCD 18bit interface for 3-Lane LVDS LCD Module.

[Case 1]

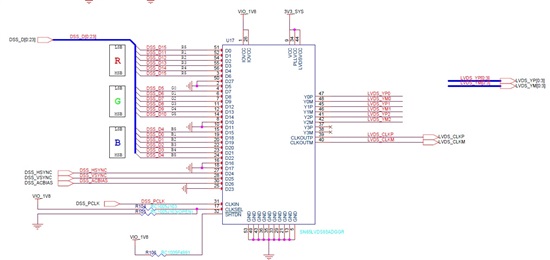

H/W was designed for 4-lanes LVDS LCD Module using SN65LVDS93ADGGR.

I think that HW can't support without changing DSS_DATA BUS for 18 bit. ( with lefting open Y3P & Y3M of SN65LVDS93ADGGR)

DISPC_CONTROL Register can be set 18-bit mode.

Can LVDS display normally under 18-bit mode setting(by DISPC_CONTROL)/Open pin(Y3P/Y3M) conditions?

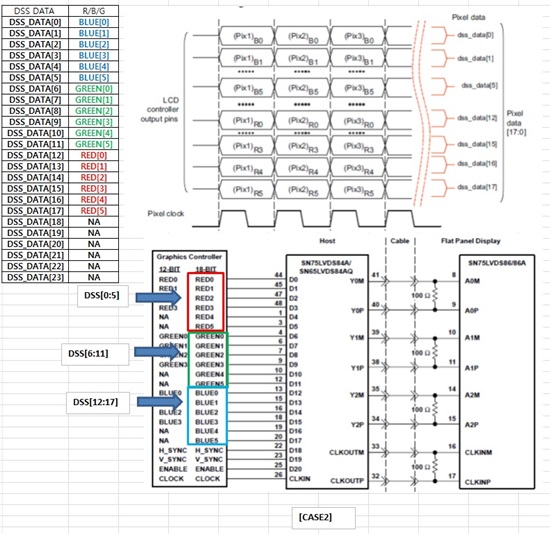

[CASE2]

I will change the schematic as below(or attached)

I want to know whether DSS_BUS mapping is correct for 18bit RGB or not .

Is this solution correct?

If yes, Could you inform registers which will be changed for 18-bit interface?

7635.DM3730_LCD Interface_20130613.xlsx

Thanks