Hello Casey,

Xiaopeng reported the black screen issue, I located the issue is related with 0x28 register value. The value showed the device don’t go to normal mode(0x19) and keeping in forward channel disable mode(0x20) after the system power up, fail rate 1/15000, and the issue repeatability rate is 100% in the special system(specific 947 and 948).

Can you help to support on this issue?

System block as below:

I have confirmed debug result as below:

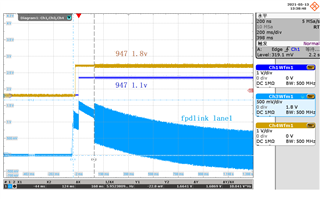

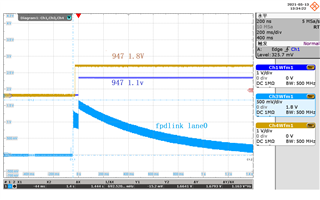

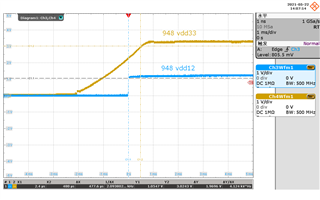

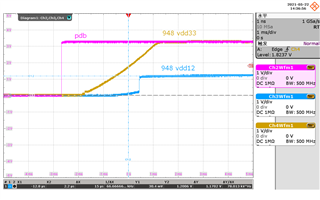

- System power sequence(947 and 948) is correct.

- The issue can’t be eliminated when turning off/on 947 and maintaining 948 power supply.

- STP cable maintaining connecting, the issue can be eliminated when turning off/on 948 and maintaining 947 power supply.

- The issue can’t be eliminated When disconnecting/reconnecting the STP cable and turning off/on the 948 power supply at the same time and maintaining the 947 power supply.

- When maintaining system power supply, and pull low/high 948 PDB, the issue can be eliminated.

- When maintaining system power supply and reset 948 by 0x01[0] bit, the issue can’t be eliminated.

- When maintaining system power supply and reset 948 by 0x01[1] bit twice times(once time, issue can’t can be eliminated), the issue can be eliminated.

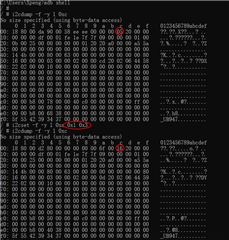

- I have tried to write the correct value into 948 0x28 register manually, but this register can’t be operated.

- The 948 register map in attachment.