Part Number: TCAN4550-Q1

Other Parts Discussed in Thread: TCAN4550

Hi Team,

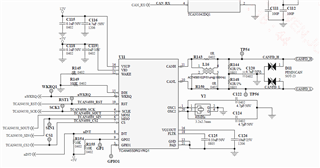

There is a good new that DIN TCAN4550-Q1

Please help check this SCH & layout, THX

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/138/4251.APA_2D00_1GBR_2800_06162021_2900_.7z1680.APA_20210616.pdf