Other Parts Discussed in Thread: 66AK2G12, SN74AHC541

Hi,

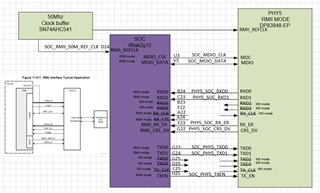

In my new design the PHY DP83848-EP is connected to the FPGA (Xilinx Artix ).

The X1 50Mhz reference clock is provided from the FPGA IO to the PHY to X1 pin 34.

The Datasheet requires clock to be stable for 167mS (table 45.7.1 pag 14 )

I assume the requirement is to have the reference clock toggling before power up and 167mS after power up.

However when sourcing the reference clock from FPGA it takes time the FPGA to have clock out since the FPGA must be configured (87 to 200mS ) all this time the IO floats.

So my suggested solution is to hold the reset of the PHY asserted at power up and during FPGA configuration. Only after the FPGA is up starting to output the reference clock to the PHY, only then the PHY is taken out of reset.

Does this method comply to the request having stable clock prior to power up?

Thanks

Avner