Other Parts Discussed in Thread: DP83825I

This is actually a continuation of another thread that I had started and has since been locked. I'm not sure why. The problem was not resolved and not that much time had elapsed.

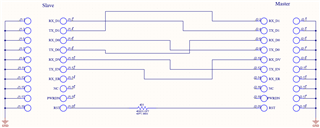

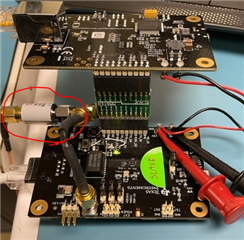

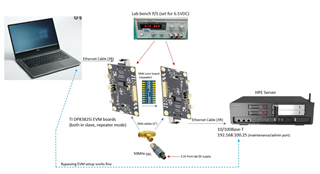

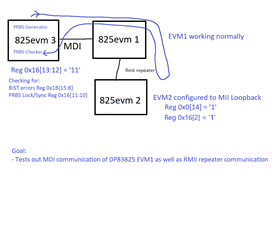

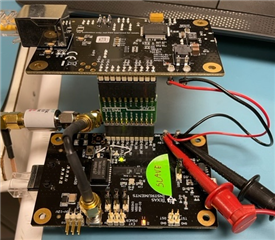

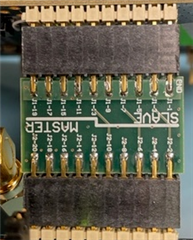

When the above thread was last active, I had been unable to connect two EVM boards together to form a repeater per the available application info for the chip and eval board. After numerous back-forths in the previous forum thread and a TI tech support phone call, it was suggested that I create a custom, impedance matched, trace length matched interface between the two EVM boards so as to try to maximize RMII signal integrity. I feel that I was able to do that and a pic of the result is below. In the end, it is still not working even after trying both a "MASTER>SLAVE" and "SLAVE>SLAVE w/ext 50MHz clock" configurations. I can still not get a 10/100Base-T connection to go through. All symptoms are the same as before (previous thread where I was using a homemade cable connection).

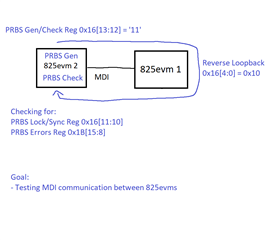

I first tried connecting a master configured board to a slave configured board and fed the master's 50MHz clock output to the slave. No joy. Then I connected two slaves together and fed an external clock to both. Clock specs: 25ppm, 2.5nS rise, 1pS jitter. Nothing. I tried resetting one and/or both boards on multiple occasions after power up.

I have both (slave) EVM boards strapped the same, including repeater mode. I am not changing any register settings after boot up. Register reads tell me straps are set correctly and that both ends are detecting a good link. When I send pings from a PC on one side to the fixed IP device on the other side, I see activity LEDs on the EVMs flash and I see data activity on the TX related signals at the RMII interface but nothing on the RX related signals.

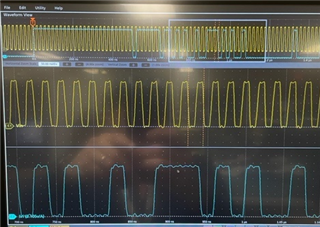

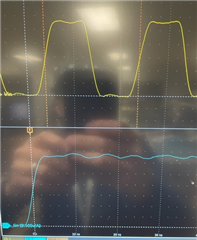

Below is the TX-D1 & CLK from the send side (when I issue IP pings)

Below is a zoomed in view of the CLK and rising edge of TX_EN

I'm really at a loss here and could use some help.