Part Number: SN65LVDS93

Hi Team,

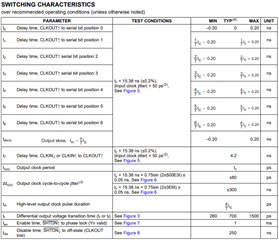

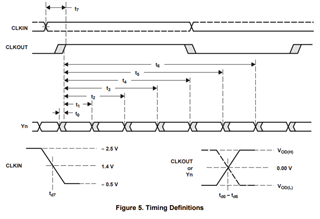

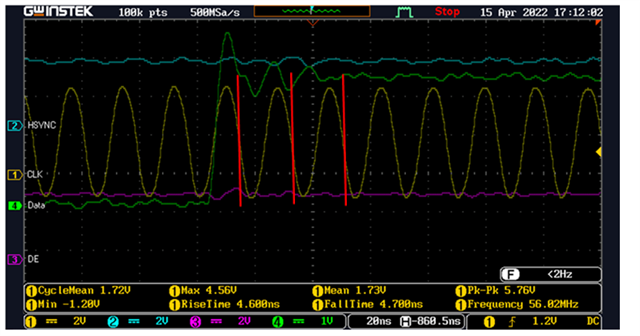

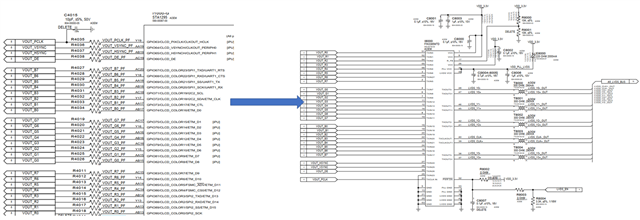

For SN65LVDS93 A version and non-A version, I assume that they are p2p compatible. The main difference is PCLK spec. Our application PCLK = 55MHz, I think we can use both of them. But when we used non-A version, the panel pattern will be abnormal. Can you help let me know which part should we need to try?

Regards,

Roy