Part Number: DP83867IR

Hi all,

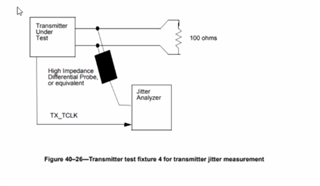

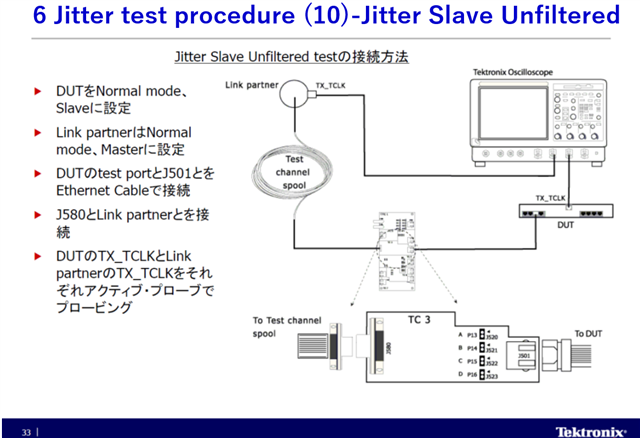

My customer prepares two of the same boards on which the DP83867IRRGZ is mounted and connects them via a fixture to conduct a compliance test.

In the Jitter test, if the DUT can be linked with the link partner with the setting of Test Mode 2 or Test mode 3, will the LED of the DUT light up?

Registers related to LEDs such as LEDCR1 are left at their default settings.

For example, in the case of "Jitter Master Unfiltered setting" in the explanation of Tektronix, DUT is set to Test mode 2, Link partner is set to Normal and Slave setting. Is there any problem with the following register settings?

Or does the Link partner set Test mode 3?

Master side (DUT):

1000 Base Test Mode 2 with TX_TCLK:

Reg 0x001F = 0x8000 // reset PHY

Reg 0x0000 = 0x0140 // 1000 Base-T Mode

Reg 0x0010 = 0x5008 // forced MDI Mode

Reg 0x0009 = 0x5B00 // Test Mode 2, Master

Reg 0x0025 = 0x0480 // output test mode to all channels

Reg 0x0170 = 0x81F // output clk a

Reg 0x00C6 = 0x0010 // proprietary

Slave side (link partner):

Reg 0x001F = 0x8000 // reset PHY

Reg 0x0000 = 0x0140 // 1000 Base-T Mode

Reg 0x0010 = 0x5008 // forced MDI Mode

Reg 0x0009 = 0x1300 // Normal, Slave

Regards,

Toshi