Other Parts Discussed in Thread: DP83822H, DP83825I

Good Evening,

We are experiencing an issue with some TLK106 PHYs when powering up at elevated temperatures. We have multiple boards, each with 7 PHYs installed, and are seeing an average of 10-15% of the PHYs failing when powering up at 50C. The remaining 85-90% have no issues, even with power cycles up to 90C ambient. The problem PHYs will power up fine around 45C and will run properly up to at least 90C without any issues. But if we power cycle the board, the problem PHYs will fail to boot.

The symptoms seem very similar to https://e2e.ti.com/support/interface-group/interface/f/interface-forum/532984/tlk105-tlk106-in-ethercat-network-doesn-t-start-at-temperatures-over-35-c, but there are some notable differences in our design.

Design details:

- 7 x TLK106 PHYs

- MACs instantiated in Xilinx Zynq SOC

- AVDD = VDD_IO = 3.3V

- RMII mode

- XI = 50MHz, 3.3V, generated from Zynq

- Individual MDIO connections between each MAC and PHY

The 50MHz reference clock is generated by the Zynq programmable logic. The Zynq comes up less than 5ms after the PHYs are powered, but the loading/configuration of the programmable logic into the FPGA is taking upwards of 1700mS (yeah, 1.7 seconds). Consequently, the reference clock into XI is not stable until about 1.7 seconds after the PHY internal POR is de-asserted. We are holding \RESET low for another ~1.5 seconds after XI is stable while the linux operating system boots.

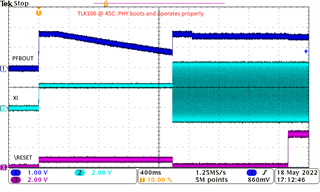

On the problem PHYs, we see the PFBOUT 1.55V supply start decaying linearly starting about 250ms after power-on. The slope of that linear decay appears to be directly related to ambient temperature; the higher the temperature, the steeper the slope. It appears that if PFBOUT only drops to 0.70V or so by the time that XI starts, PFBOUT will reset to 1.55V and the PHY will recover (see 1st scope shot). However, if the PFBOUT drops any further (either due to steeper temperature slope or further delayed XI start), PFBOUT will stay low and the PHY will be unresponsive (see 2nd scope shot). Notice the steeper slope.

Once unresponsive, neither asserting \RESET or writing PFB_OFF via MDIO can revive the PHY (it appears the 1.55V powers the internal registers, so MDIO is dead).

On the working PHYs, we do not see any PFBOUT decay with power cycles up to 90C.

Questions:

- Is there a firm requirement for XI to be stable within Xms after/before AVDD power-up? I don't see any such timing requirement in the datasheet. Note: I was able to hack one PHY to delay AVDD, such that the clock was stable before power-up. With that hack, the problem PHY powered up perfectly.

- Is it known why this behavior is only present on some (10-15% of my sample size) PHYs? No correlation I can deduce from our boards; on one board, PHY1 and PHY7 are problematic, on another, PHY2 is problematic. It is seemingly random which PHYs will tolerate the condition. All PHYs in use are from the same lot/reel.

- Is there any workaround given the constraints of my design (XI comes 1.7sec after AVDD)? Asserting \RESET does not work.

- If this behavior is understood, is there a chance TI could screen the parts that will work in my application?

Thank you in advance for the help. Please forgive my less-than-perfect scope shots. The XI input is actually 0-3.3V, but given the challenge of scoping at 60C ambient in a small chamber, my lousy ground connection makes for an inaccurate voltage measurement of the 50MHz clock.

-Kyle, BSEE Avionics Design