Hi Team,

We are using DS110DF410SQ IC in our design and we are not getting the video output as expected ( we are using it for ARINC 818 video stream)

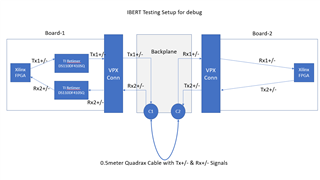

I have attached the overall setup and how we are debugging this, and we have few observation related to this debug

We have Xilinx FPGA in the board and since we were not able to get the required video we are into debug mode and xilinx support IBERT were we can run the random PRBS patter to see the behavior of the signal Transmission and reception in the FPGA

So here we observe

Observation 1:

when Both Tx1 to Rx 1 path and Tx2 to Rx2 path is enabled ( PRBS data transmission) board 1 & 2 observe the errors at the respective Rx

Observation 2:

When Tx1 to Rx 1 path is disable ( no PRBS data transmission) then the board 1 (Rx2) will receive the data properly without any issue

we are still debugging and would get input from TI what might be the issue and how can we fine tune this with retimer configuration

Note :

we have total 8-Tx & Rx channels and we see this issue only in two channels

Seperate Retimers for Tx and Rx is used

Regards,

Karthik