Other Parts Discussed in Thread: TUSB1002

Our latest design, MB used TUSB1002A,

SW board co-lay TUSB1002 and TUSB1002A, and implement TUSB1002 on SW board now.

Could you help to clarify these questions below,

- Do the feedbacks of the below Q1,Q2 apply to both TUSB1002 and TUSB102A?

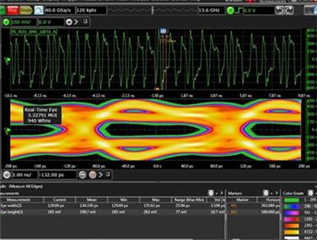

- We’re trying to adjust the eye diagram which is not good. Can you tell us which table that we can refer for eye diagram adjusting if “mode/CFG1/CFG2” must be set as “R, 0, 0“ that mean the “Table 3. VOD Linear Range and DC Gain” isn’t working for the PCIe mode, there is only “Table 2. EQ Configuration Options for 1200mV Linearity 0 dB DC Gain Setting” that we can refer to adjust for eye diagram improvement ?

Please confirm, and let us know if there are any document or table on the datasheet that we can refer to.

3: Could you please provide the validating report of these two redrives including which parameter TI has set in these two chips’ validation. That will be helpful to our SI team.