Part Number: TCA9555

Other Parts Discussed in Thread: TCA9534A, TMP275, TM4C129ENCPDT, TCA4307

Hi,

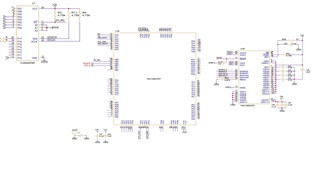

I am using TCA9555 three chips connected to same I2C bus and another I2C Temperature sensing chip TMP275AID. So basically, I have total four I2C chips on board such that three of them are TCA9555. All TCA9555 chips are with default configurations and used as input ports. So I have not changed the default configuration register. I am using TM4C129ENCPD Cortex ucontroller from TI.

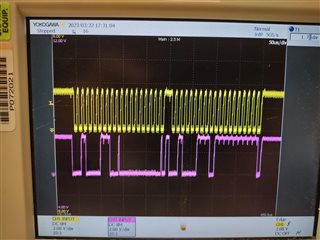

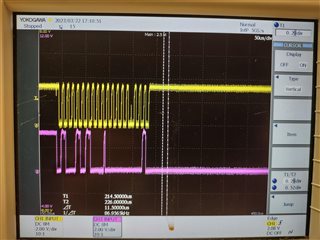

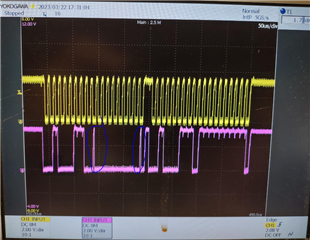

I see the SDA line will not come back High time to time randomly. Please keep in mind the code I have written is same as of earlier project where same uController was talking to TCA9534A chip and we had never seen any problem.

I confirm we have 4.75kR pull-ups on SCL and SDA lines. When I scope the SDA and SCL lines, I see time to time the SDA line will not come back High (From Low to High).

I removed two TCA9555 chips and left only one TCA9555 chip on board and I still see the same problem.

The SCL is running at 100kHz.

The addresses set on A2:A1:A0 lines of the four chips are;

Chip1 (TCA95555): 0b000

Chip2 (TMP275AID): 0b010

Chip3 (TCA95555): 0b011

Chip4 (TCA95555): 0b100

Any idea ?

Thanks