Other Parts Discussed in Thread: TUSB214

Dear TI experts,

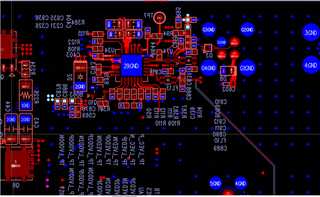

My customer made their PCB with TUSB214-Q1.

Actually they tested with TUSB214 EVM, and they drew the schematic just like they tested with EVM.

(I posted E2E thread while testing.)

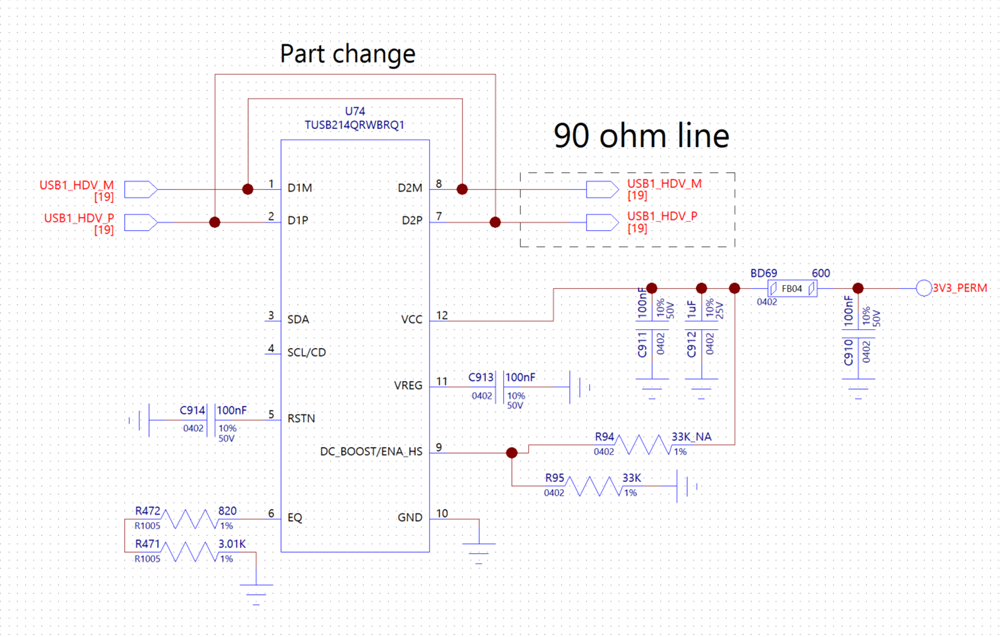

but the sample do not working now. Could you review the schematic first?

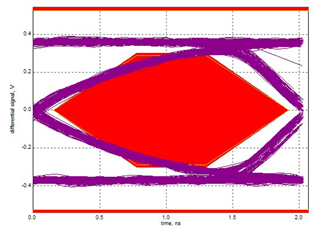

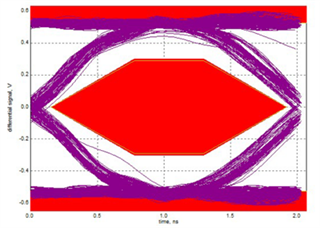

the diagram below is not applying TUSB214.

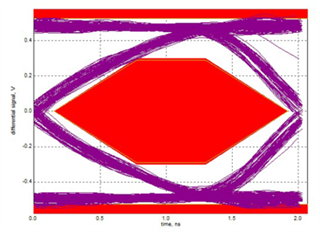

the diagram below is applying TUSB214.

and here are the questions.

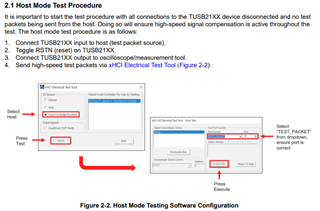

1. last time I found that VCC should be applied first before USB communication is started. (TUSB214 does now work if USB communication start first.)

Is there any minimum time between applying VCC and start USB communication?

2. if USB memory attached, SCL is 3.3V and SDA is 2.8V. but if I remove USB drive, SCL and SDA is 0V.

Is it related to not-working situation?

Please check this issue. Thanks.

Best regards,

Chase