- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear team

Regarding of the following questions about FPD-link, Could you help to recommend?

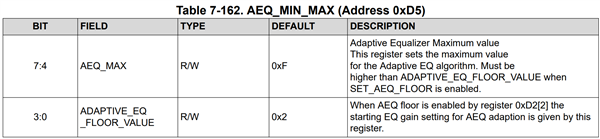

1. What is the difference between AEQ setting Full range and disable?

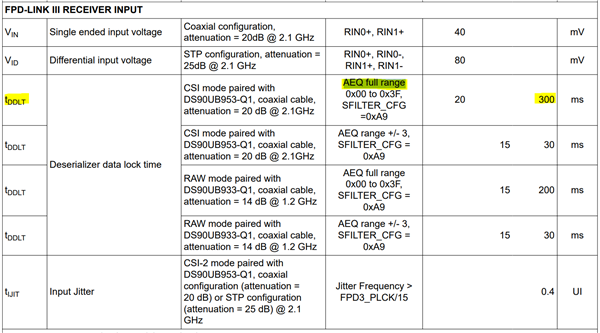

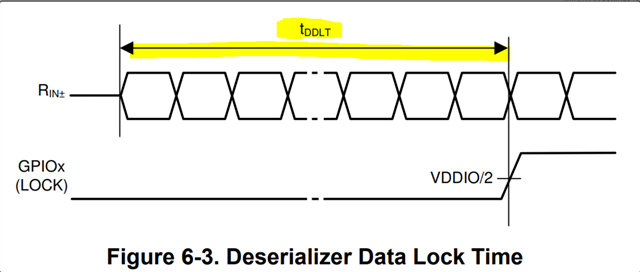

2. The current AEQ setting is Full range (set 0xD5 = 0x0E, EQ=0~14 full range). That is to say, lock out high will be after 300ms(TDDLT) at most, right?

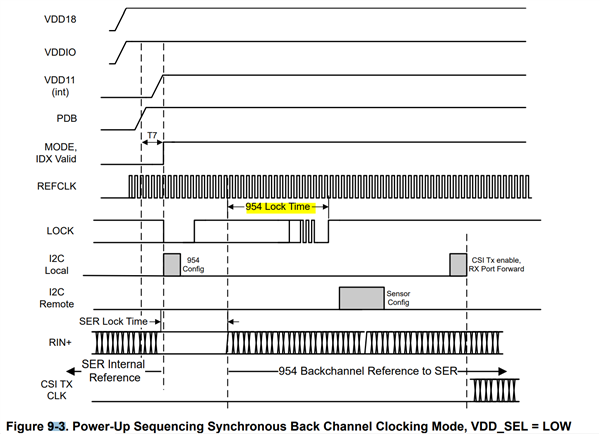

3. In 953/954 initial, how long is the lock time defined? (sync mode)

Many thanks

Denny

Hi Denny,

1. What is the difference between AEQ setting Full range and disable?

The AEQ setting is full range is 0-14, but you can make it narrower for a faster lock time in register 0xD5. If you want to narrow the AEQ range, it is recommended to determine what that range is using the MAP tool (see user guide here). If by disable you mean manually setting an EQ and strobe position, please see this E2E.

2. The current AEQ setting is Full range (set 0xD5 = 0x0E, EQ=0~14 full range). That is to say, lock out high will be after 300ms(TDDLT) at most, right?

If you have the AEQ setting in full range (0xD5 = 0xE0) then yes the max lock time is 300ms for that specific condition (CSI mode paired with DS90UB953, coax cable, attenuation = 20dB at 2.1GHz). It is also assuming that you have set 0x41 SFILTER_CFG to 0xA9 for optimal startup.

You can read more about the AEQ settings in this MAP tool app note: https://www.ti.com/lit/an/snla301/snla301.pdf or refer to section 7.4.9.2 in the 954 datasheet.

3. In 953/954 initial, how long is the lock time defined? (sync mode)

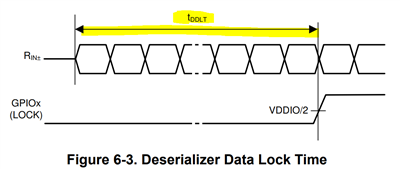

The lock time depends on what mode you are in and what cable you are using. We specify the typical and max lock times in the datasheet specifications, which you can see in the screenshot you have taken.

Regards,

Cindy

Hi Cindy

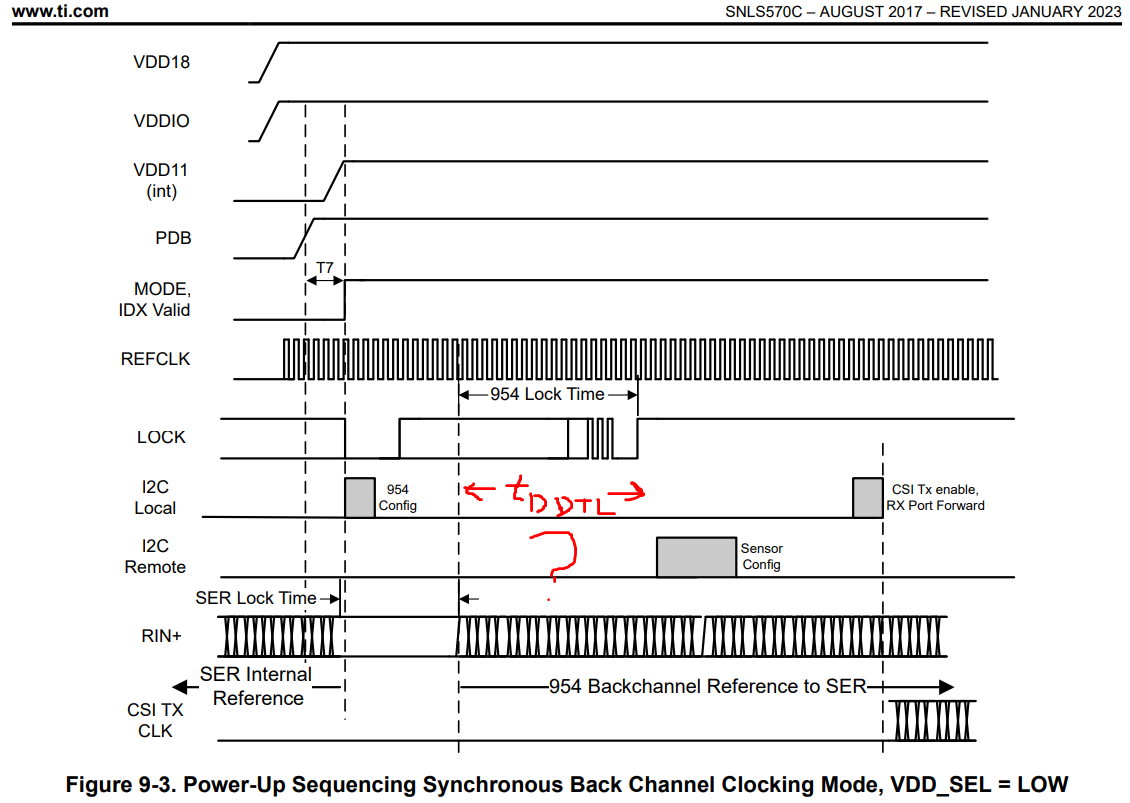

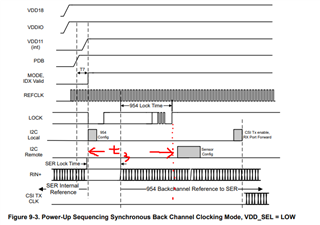

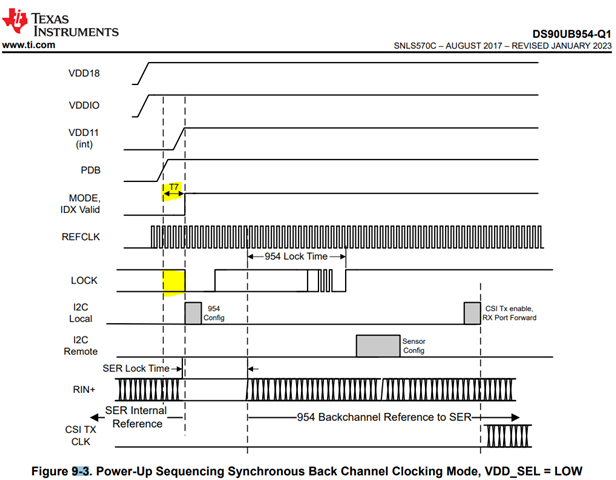

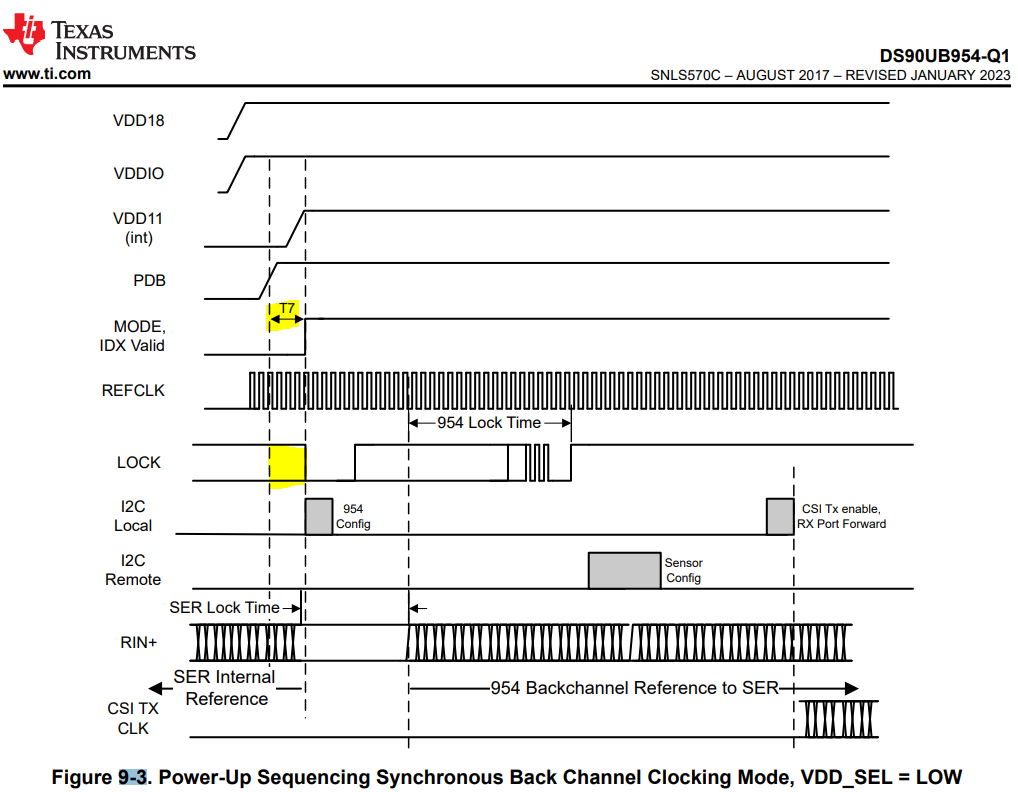

For the question 3 , May I know where is the tDDLT correspond to Figure 9-3 ?

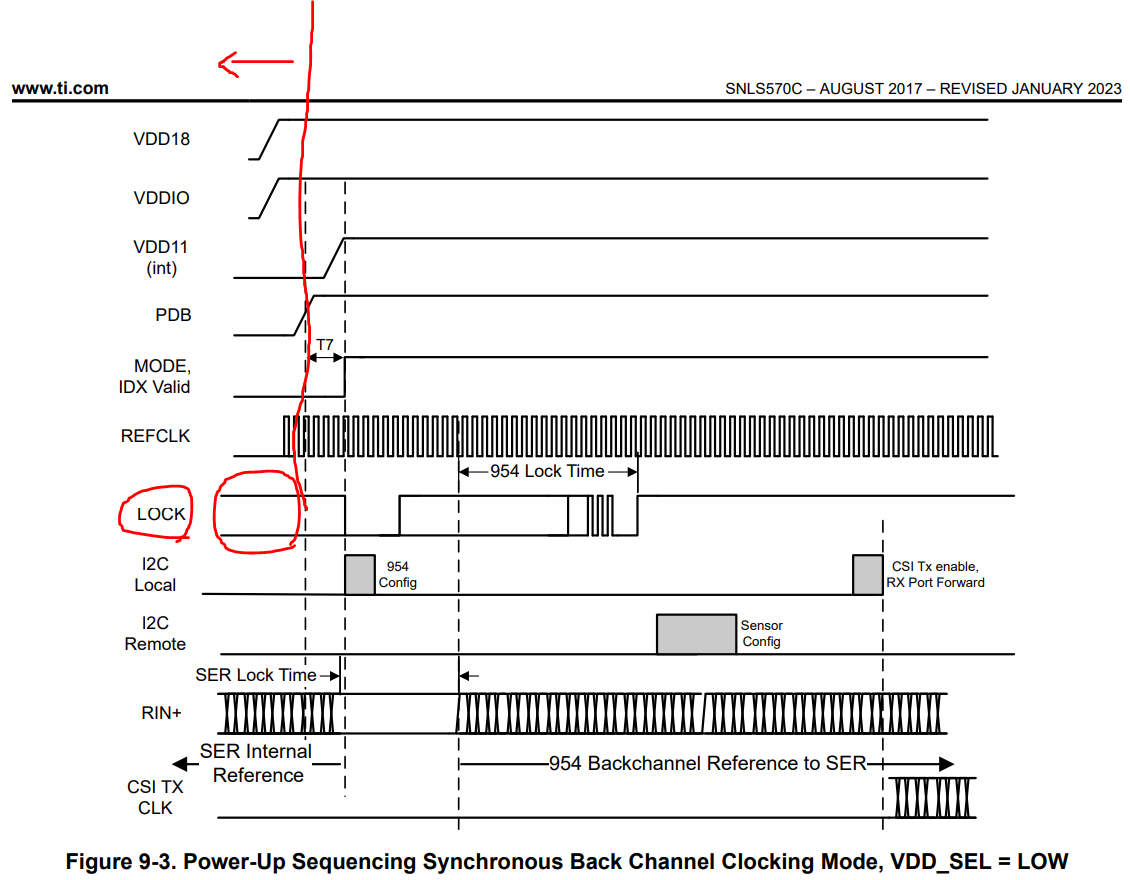

2. For synchronous mode, Did the LOCK pin high level before power up(VDD18、PDB、VDDIO)?

Many thanks

Denny

Hi Denny,

For tDDTL, yes it corresponds to "954 Lock time" in the diagram.

LOCK should not high before power supplies are up. We will correct it in the future datasheet revision.

Regards,

Cindy

Hi Cindy

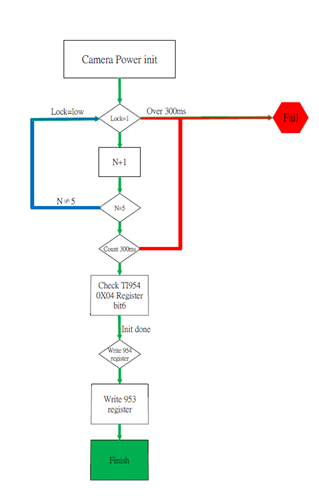

The customer use the software to check the status of LOCK signal. They have questions about the code and timing of detection.

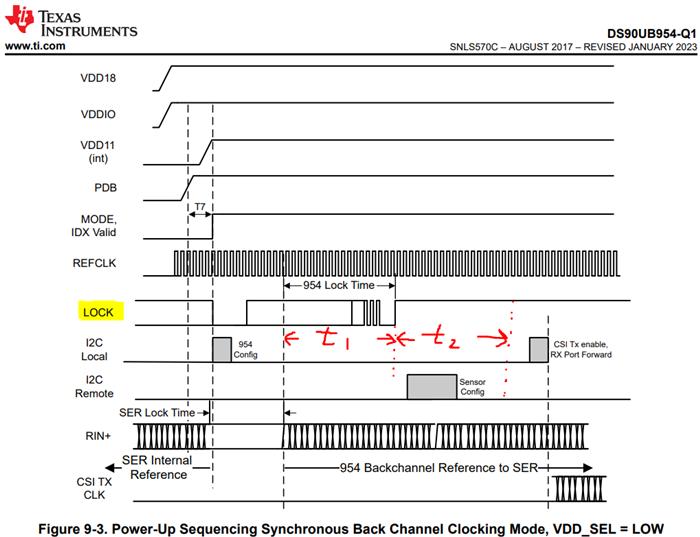

1. They want to check the status of LOCK. Which timing is better? t1 or t2?

2. This is the code behavior. Could you help to check if the behavior reasonable.

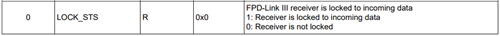

1. Check the status of LOCK. Check the 954's REG(0X4D) bit 0.

They will check REG(0X4D) bit 0 every 20ms. And they will check 5 times in 100ms time period.

A.If the 5 times alway read 1(count five times). They will judge the Lock successful.

B.If the 5 times alway read unlock,they will re-check the REG(0X4D) bit 0. If at 300ms period can't count five time.

They will judge the Lock fail.

Many thanks

Denny

Hi Denny,

1. They want to check the status of LOCK. Which timing is better? t1 or t2?

You should check the LOCK status at T2 and onwards since LOCK may still be coming up during T1. This register is clear on read, so I suggest reading it right after start-up to clear it before monitoring.

2. This is the code behavior. Could you help to check if the behavior reasonable.

I would suggest monitoring the LOCK_STS_CHG bit in 0x4D bit[4]. Since the register is clear on read, this bit will get flagged if the LOCK status ever dropped between read times. A LOCK status change would indicate that the link is unstable. It is important that LOCK_STS_CHG remains 0 throughout operation.

Regards,

Cindy

Hi Cindy

Thanks for your suggestions.

You should check the LOCK status at T2 and onwards since LOCK may still be coming up during T1. This register is clear on read, so I suggest reading it right after start-up to clear it before monitoring.

=>You would suggest check the LOCK status at T2 by checking the LOCK_STS_CHG bit in 0x4D bit[4] right?

but may I know after 954 config, How many delay time(t3) need to wait?

For the flow chart of lock detection, Did you have any recommend?

Many thanks

Denny

Hi Denny,

You would suggest check the LOCK status at T2 by checking the LOCK_STS_CHG bit in 0x4D bit[4] right?

You can first check to see whether LOCK = 1 in Reg 0x4D[0] then monitor LOCK_STS_CHG in 0x4D[4] to make sure that the lock status does not change.

but may I know after 954 config, How many delay time(t3) need to wait?

t3 will depend on the SER lock time and DES lock time as shown in the diagram. The DES lock time is given in the 954 datasheet specifications. The SER lock time is the time it takes to for the serializer to lock after exiting PDB. You would need to determine this based on your specific system and serializer power up sequence timing. Please refer to the serializer datasheet for more information about the power-up sequence timing.

For the flow chart of lock detection, Did you have any recommend?

So you read LOCK 5 times and consider LOCK to be stable if each time it reads 1, correct? This should be fine, but you can also check the LOCK_STS_CHG bit as well to see whether LOCK ever dropped between reads. In general, register 0x4D can be monitored throughout operation to check for errors.

Regards,

Cindy

Hi Cindy

Thanks for your reply. But they have another questions.

May I know when the lock pin will high after power up? Did they have spec?

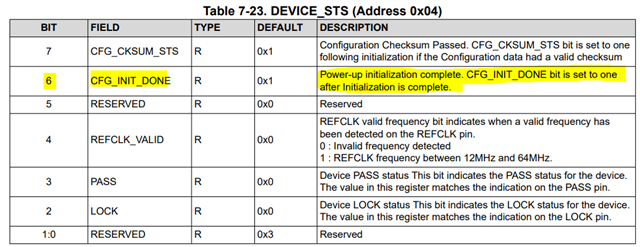

2. For the 0x04[6] CFG_INIT_DONE, which timing we could read this REG for checking power-up initialization complete?

Many thanks

Denny

Hi Denny,

May I know when the lock pin will high after power up? Did they have spec?

As I mentioned above, the diagram in the current datasheet is not accurate. LOCK will be low if the power supplies are not all up yet. In synchronous mode, 954 LOCK will go high at the end of the 954 lock time. LOCK should not be monitored until after the 954 lock time has passed.

2. For the 0x04[6] CFG_INIT_DONE, which timing we could read this REG for checking power-up initialization complete?

This bit gets set to 1 once all of the default configurations are loaded into the device. It would be set after the device is powered on, so after T7. Note that it is not an indication of LOCK being high.

Regards,

Cindy

Hi Cindy

As I mentioned above, the diagram in the current datasheet is not accurate. LOCK will be low if the power supplies are not all up yet. In synchronous mode, 954 LOCK will go high at the end of the 954 lock time. LOCK should not be monitored until after the 954 lock time has passed.

=>I know should not be monitored LOCK before 954 and 953 lock come completely.

1. So the timing of 954 config which is PDB power up and delay T7?

Many thanks

Denny

Hi Denny,

1. So the timing of 954 config which is PDB power up and delay T7?

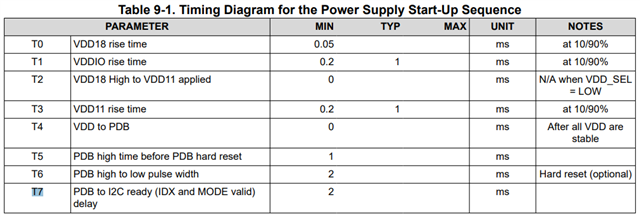

I am not sure I understand your question completely - are you asking about the timing between PDB being powered up and the start of 954 config? After PDB is high, you must wait a minimum of 2ms (T7) in order for the MODE and I2C address to be valid. After this delay you will be able to send local I2C transactions and configure the 954. Does this answer your question?

Regards,

Cindy